#### PARALLEL COMPUTING LABORATOR

# Towards Provably Optimal Parallel Systems

Krste Asanovic UC Berkeley

MATEO-2012, Barcelona June 29, 2012

- Berkeley Par Lab ending (Wrap May 23, 2013).

- Talk today is early look at next project, ASPIRE

- Faculty participants:

- Elad Alon

Circuits

- Jim Demmel

Algorithms

- Armando Fox

Programming Systems

- John Wawrzynek

Reconfigurable

#### Even if <<1% of programmers understand it</p>

- Humanity's capabilities limited by biggest machines running most efficient code.

- Natural user interfaces are performance limited.

- More efficient primitives support more sloppy code above (e.g., Lua game scripting, or mashups built on top of warehouse-scale computer services)

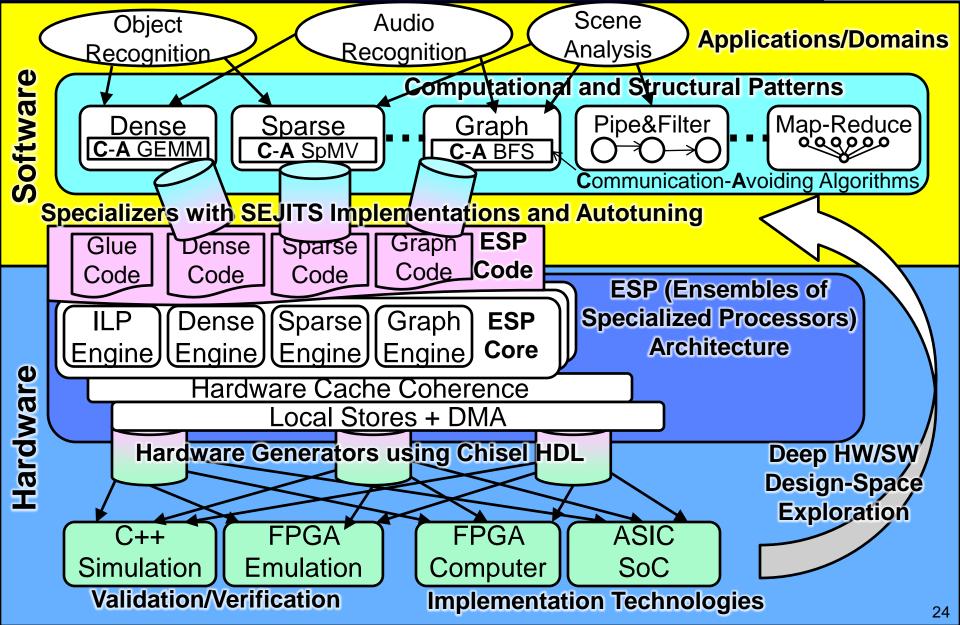

Efficient systems => Parallel systems

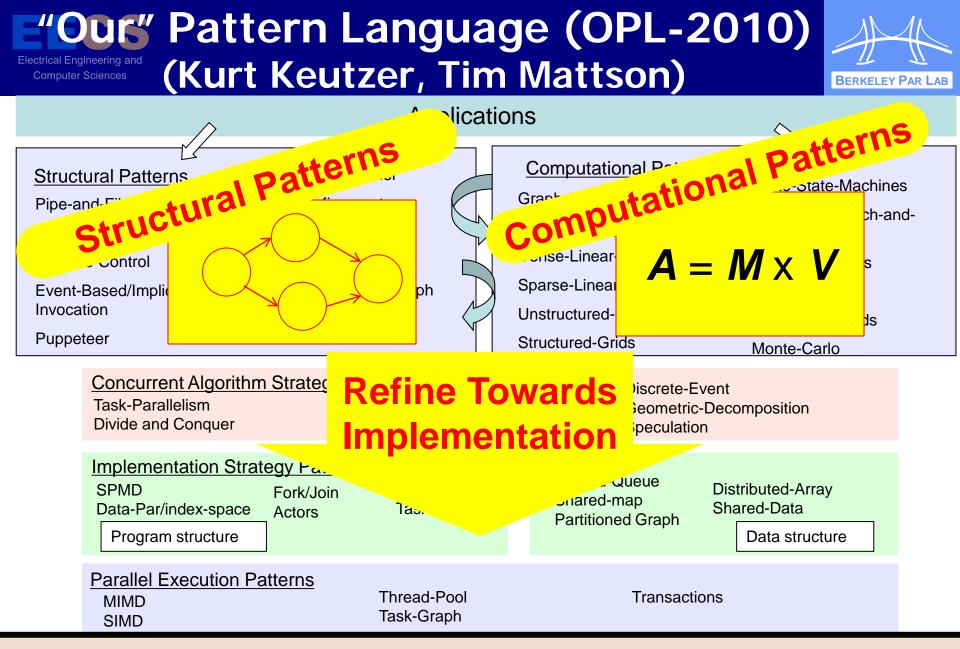

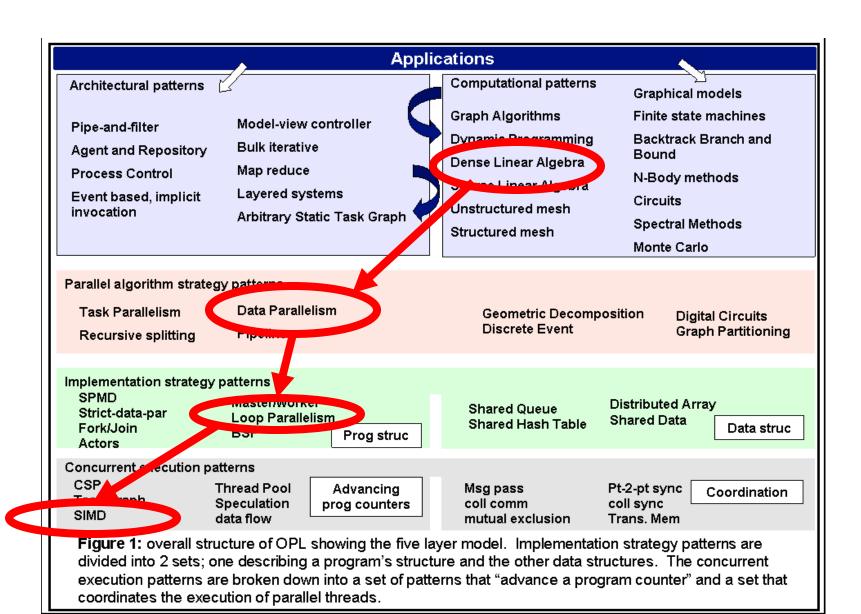

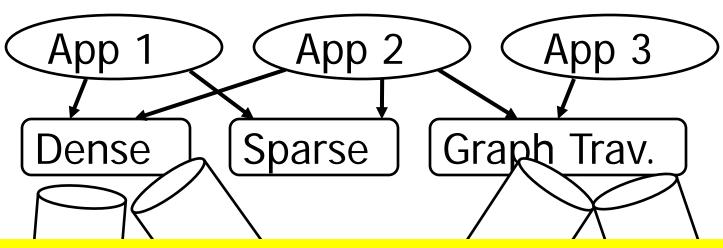

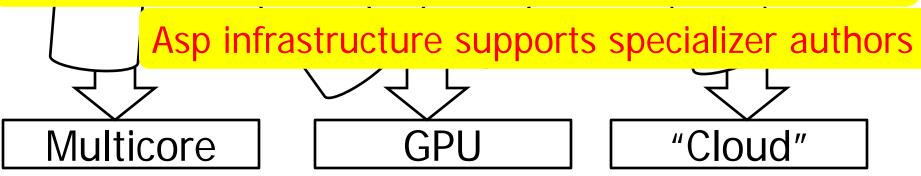

- Organize software around parallel patterns

- Maximize reuse since patterns common across domains

- Communication-Avoiding Algorithms for patterns

- Implement each pattern with highly efficient specializers using SEJITS-based autotuners

- Programmer composes functionality at high-level using productivity language

- System composes resource usage using 2-level scheduling: 1) Tessellation OS at coarse-grain and 2) Lithe user-level scheduler at fine-grain

# Electrical Engineering and Computer Sciences Motif (nee "Dwarf") Popularity Motif (nee "Dwarf") Popularity Computer Sciences (Red Hot Blue Cool) Blue Cool)

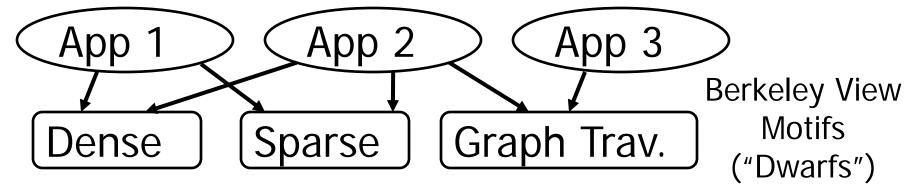

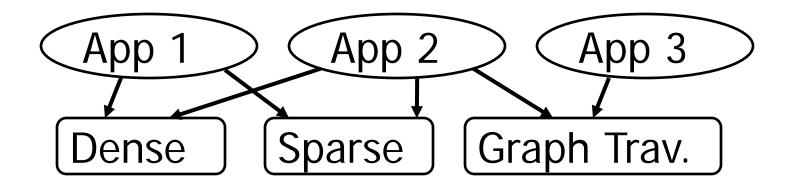

#### How do compelling apps relate to 13 motifs?

|    |                    | Embed | SPEC | DB | Games | ML | CAD | НРС | Health | Mage | Speech | Music | Browser |

|----|--------------------|-------|------|----|-------|----|-----|-----|--------|------|--------|-------|---------|

| 1  | Finite State Mach. |       |      |    |       |    |     |     |        |      |        |       |         |

| 2  | Circuits           |       |      |    |       |    |     |     |        |      |        |       |         |

| 3  | Graph Algorithms   |       |      |    |       |    |     |     |        |      |        |       |         |

| 4  | Structured Grid    |       |      |    |       |    |     |     |        |      |        |       |         |

| 5  | Dense Matrix       |       |      |    |       |    |     |     |        |      |        |       |         |

| 6  | Sparse Matrix      |       |      |    |       |    |     |     |        |      |        |       |         |

| 7  | Spectral (FFT)     |       |      |    |       |    |     |     |        |      |        |       |         |

| 8  | Dynamic Prog       |       |      |    |       |    |     |     |        |      |        |       |         |

| 9  | Particle Methods   |       |      |    |       |    |     |     |        |      |        |       |         |

| 10 | Backtrack/ B&B     |       |      |    |       |    |     |     |        |      |        |       |         |

| 11 | Graphical Models   |       |      |    |       |    |     |     |        |      |        |       |         |

| 12 | Unstructured Grid  |       |      |    |       |    |     |     |        |      |        |       |         |

| 13 | Monte Carlo        |       |      |    |       |    |     |     |        |      |        |       |         |

#### Concurrency Foundation constructs (not expressed as patterns)

Thread creation/destruction Process creation/destruction Message-Passing Collective-Comm. Point-To-Point-Sync. (mutual exclusion) collective sync. (barrier)

#### **EECS** Electrical Engineering and Computer Sciences Mapping Patterns to Hardware

## Only a few types of hardware platform

#### Electrical Engine and Computed fine reasonable low-level mappings

10

# aka. "Stovepipes"

Allow maximum efficiency and expressibility in specializers by avoiding mandatory intermediary layers

#### Par Lab Stack Overview

12

- Technology scaling slowing down/stopping

- No savior device technology on horizon

- Parallelism was one-time gain, using more, lower-performance cores for better energy efficiency

- Simpler general-purpose microarchitectures

- Limited by smallest sensible core

- Lower Vdd/Frequency

- Limited by Vdd/Vt scaling, errors

- Now what? Only option appears to be more specialized hardware running more optimized software.

- What is the best we can do?

- For a fixed target technology (e.g., 7nm):

- Can we prove a bound?

- Can we design an implementation to approach that bound?

- => Provably Optimal Implementations!

\*ASPIRE: Algorithms and Specializers for Provably Optimal Implementations with Resiliency and Efficiency

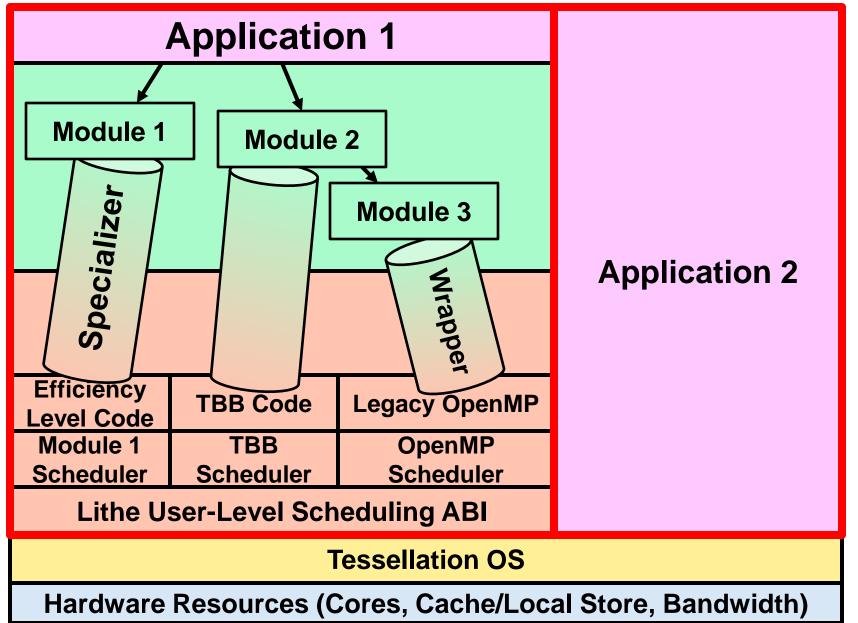

- 1. Arithmetic (FLOPS)

- 2. Communication: moving data between

- levels of a memory hierarchy (sequential case)

- processors over a network (parallel case).

## Electrical Engineering and Computer Sciences (Jim Demmel & BEBOP Group)

- Communication = moving data, between levels of memory or between processors over a network

- Cost of communication >> cost of arithmetic

- True for cost = time, or cost = energy per operation

- Cost gap growing over time

- Goals

- Identify lower bounds on *communication* required by widely used algorithms

- Many widely used libraries (eg Sca/LAPACK) communicate asymptotically more than necessary

- Design new algorithms that attain lower bounds

- Possible for dense and sparse linear algebra, n-body, ...

- Big speedups and energy savings possible

## EECS Ex: Lower bound for all "direct" Internal Sciences

• Let M = "fast" memory size (per processor)

#words\_moved (per processor) =  $\Omega$ (#flops (per processor) / M<sup>1/2</sup>)

#messages\_sent ≥ #words\_moved / largest\_message\_size

- Holds for

- Matmul, BLAS, LU, QR, eig, SVD, tensor contractions, ...

- Some whole programs (sequences of these operations, no matter how individual ops are interleaved, e.g. A<sup>k</sup>)

- Dense and sparse matrices (where #flops << n<sup>3</sup>)

- Sequential and parallel algorithms

- Some graph-theoretic algorithms (e.g. Floyd-Warshall)

#### Electrical Engineering and A few examples of speedups Computer Sciences

#### Matrix multiplication

- Up to 12x on IBM BG/P for n=8K on 64K cores; 95% less communication

- QR decomposition (used in least squares, data mining, ...)

- Up to 8x on 8-core dual-socket Intel Clovertown, for 10M x 10

- Up to 6.7x on 16-proc. Pentium III cluster, for 100K x 200

- Up to 13x on Tesla C2050 / Fermi, for 110k x 100

- Up to 4x on Grid of 4 cities (Dongarra, Langou et al)

- "infinite speedup" for out-of-core on PowerPC laptop

- LAPACK thrashed virtual memory, didn't finish

- Eigenvalues of band symmetric matrices

- Up to 17x on Intel Gainestown, 8 core, vs MKL 10.0 (up to 1.9x sequential)

- Iterative sparse linear equations solvers (GMRES)

- Up to 4.3x on Intel Clovertown, 8 core

- N-body (direct particle interactions with cutoff distance)

- Up to 10x on Cray XT-4 (Hopper), 24K particles on 6K procs.

- SIAM Linear Algebra Prize 2012, for best paper in previous 3 years, deriving lower bounds

- SPAA'11 Best Paper Award, for Strassen lower bounds

- EuroPar'11 Distinguished Paper Award, for asymptotically faster "2.5D" matmul and LU

- Citation in 2012 DOE Budget Request ...

President Obama cites Communication-Avoiding Algorithms in the FY 2012 Department of Energy Budget Computer Sciences Request to Congress:

"New Algorithm Improves Performance and Accuracy on Extreme-Scale Computing Systems. On modern computer architectures, communication between processors takes longer than the performance of a floating point arithmetic operation by a given **processor.** ASCR researchers have developed a new method, derived from commonly used linear algebra methods, to minimize communications between processors and the memory hierarchy, by reformulating the communication patterns specified within the algorithm. This method has been implemented in the TRILINOS framework, a highly-regarded suite of software, which provides functionality for researchers around the world to solve large scale, complex multi-physics problems."

FY 2010 Congressional Budget, Volume 4, FY2010 Accomplishments, Advanced Scientific Computing Research (ASCR), pages 65-67.

CA-GMRES (Hoemmen, Mohiyuddin, Yelick, Demmel) "Tall-Skinny" QR (Grigori, Hoemmen, Langou, Demmel)

# Electrical Engineering and Computer Sciences Optimal Systems?

- 1) Prove lower bounds on communication for a computation

- Develop algorithm that achieves lower bound on a system

- Find that communication time/energy cost is

90% of resulting implementation

- ✤ 4) We know we're within 10% of optimal

- Supporting technique: Optimize cores so that they get sufficiently low energy to ignore

#### Electrical Engineering and Computer Sciences ESP Architecture: Ensembles of Specialized Processors

- General-purpose hardware, flexible but inefficient

- Fixed-function hardware, efficient but inflexible

- Insight: Patterns capture common operations across many applications, each with unique computation/communication structure

- Build an ensemble of specialized engines, each individually optimized for particular pattern but collectively covering application needs

- Bet: Will give us efficiency plus flexibility

- Any given core can have a different mix of these depending on workload

- Optimize compute and data movement per pattern

- Dense Engine: Provide sub-matrix load/store operations, support in-register reuse

- Structured Grid Engine: Supports in-register operand reuse across neighborhood

- Sparse Engine: Support load/store of various sparse data structures

- Graph Engine: Provide load/store of bitmap vertex representations, support many outstanding requests

## **ASPIRE Initial Stack Bet**

#### Questions? Thoughts? Feedback?

- Research supported by Microsoft (Award #024263) and Intel (Award #024894) funding and by matching funding by U.C. Discovery (Award #DIG07-10227).

- Additional support comes from Par Lab affiliates National Instruments, NEC, Nokia, NVIDIA, Samsung, and Oracle/Sun.