# 2020 Architecture Research with RISC-V and Chisel

Yunsup Lee Andrew Waterman

Jonathan Bachrach, Scott Beamer, David Patterson, Krste Asanovic

### Facilitating Credible Architecture Research

- Simulators are useful for measuring cycle counts—useless for power, area, cycle time

- But microarchitects must balance all of these!

- Need an end-to-end research methodology to close the feedback loop...

- ...but traditional HW design approaches with commercial ISAs are far too tedious

#### **RISC-V Software Stack**

- GCC 4.4 with Newlib C library

- "Proxy Kernel" to support POSIX calls by forwarding to a Linux host machine

- Coming soon, Linux and ROS/Tessellation

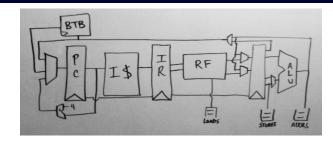

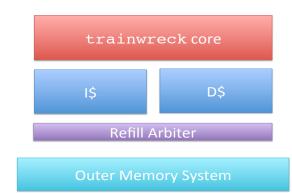

## trainwreck: A RISC-V Prototype

- Simple 3-stage pipeline with decoupled data memory interface

- 64-bit fixed-point datapath, double-precision FP

#### RISC-V ISA

|           | 31 27              | 26 22           | 21 17    | 16 12  | 11 10 9 | 7     | 6      | 0        |         |

|-----------|--------------------|-----------------|----------|--------|---------|-------|--------|----------|---------|

|           | rd                 | rs1 rs2 funct10 |          |        |         | 0     | pcode  | R-type   |         |

|           | rd                 | rs1             | rs2      | rs3    | funct5  |       | opcode |          | R4-type |

|           | rd                 | rs1             | imm[4:0] | imm[11 | :5] fi  | ınct3 | 0      | pcode    | I-type  |

|           | imm[4:0]           | rs1             | rs2      | imm[11 | .:5] fi | inct3 | 0      | pcode    | B-type  |

|           | rd                 |                 |          |        |         |       |        | pcode    | L-type  |

|           | jump offset [24:0] |                 |          |        |         |       | opcode |          | J-type  |

|           |                    |                 |          |        |         |       |        |          |         |

| inst[4:2] | 000                | 001             | 010      | 011    | 100     | 10    | 1      | 110      | 111     |

| inst[6:5] |                    |                 |          |        |         |       |        |          | (> 32)  |

| 00        | LOAD               | LOAD-FP         | MISC-MEM |        | OP-IMM  | MIS   | SC     | OP-IMM-3 | 32      |

| 01        | STORE              | STORE-FP        | AMO      |        | OP      | LU    | Л      | OP-32    |         |

| 10        | MADD               | MSUB            | NMSUB    | NMADD  | OP-FP   |       |        |          |         |

| 11        | BRANCH             | JALR            | J        | JAL    |         | SYSC  | ALL    |          |         |

- Straightforward 32-bit instruction encoding

- Supports compressed encodings and extended-length instructions

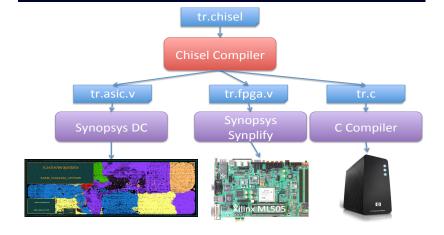

#### Chisel

- Is a Hardware Construction Language

- Is not a Hardware

Description Language:

no un-synthesizable

constructs

- Is type-safe and more expressive than Verilog

- Is embedded in Scala

## Target Machine

## Why a new ISA?

- Provide a realistic but open ISA that captures important details of commercial generalpurpose ISA designs and that is suitable for hardware implementation.

- Provide a small but complete base ISA that avoids "over-architecting" for a particular microarchitecture style or implementation technology, but which allows efficient implementation in any of these.

#### **Chisel Backends**

#### DEMO

- Hand written Trainwreck on FPGA & ASIC

- Chiseled Trainwreck on FPGA & ASIC