### ostrac<sup>.</sup>

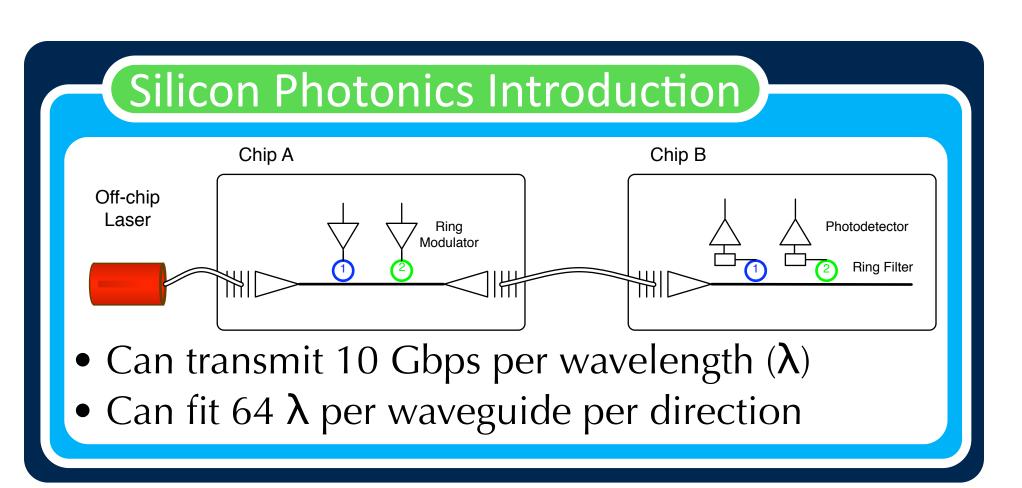

A manycore system will require tremendous bandwidth to memory, and current and projected electrical interconnects for off-chip communication may be unable to meet this challenge. In this work, we use monolithically integrated silicon photonics to construct a scalable interconnect between many cores and memory within a multi-socket system. Our interconnect also makes it possible to consider using smaller dies for cost reasons. Our design can be extended to a general template which can be configured to a particular die size and number of sockets.

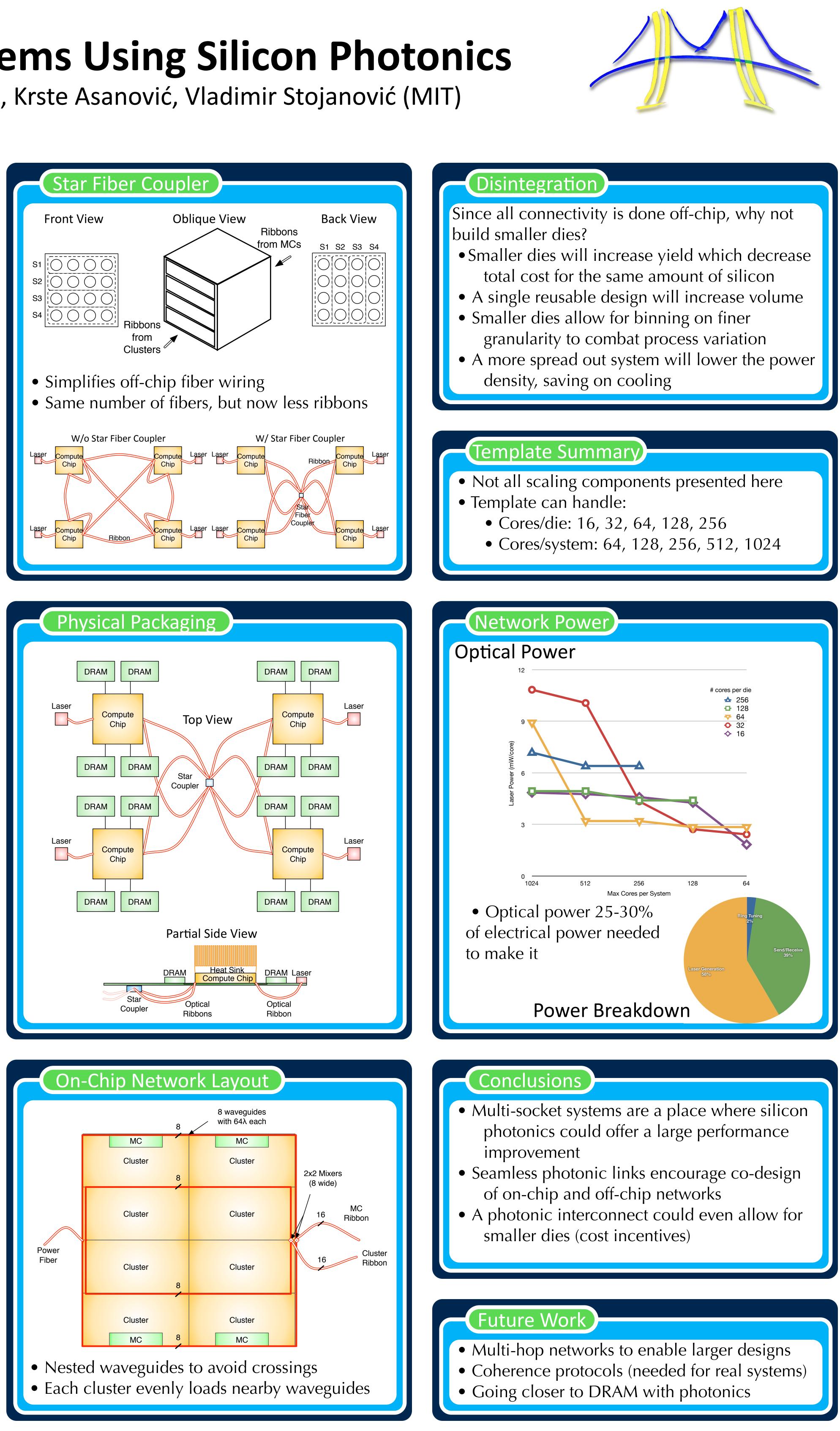

# Silicon-Photonic Components

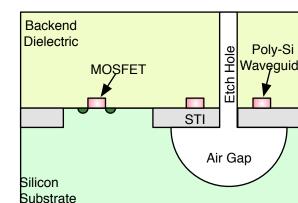

### Waveguide

• Poly-silicon on top of shallow trench isolation

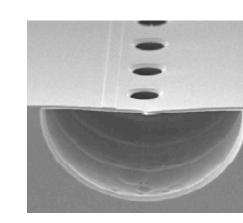

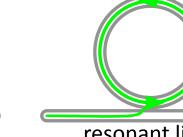

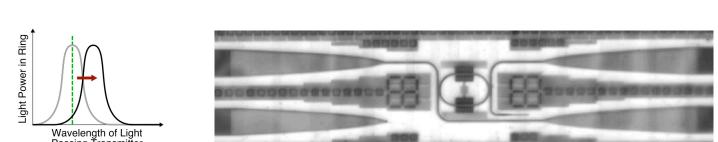

#### Resonant Ring

light not resonan<sup>-</sup>

• Rings of the correct dimensions can resonate • Can use heaters to tune rings (battle variation)

### **Ring Modulator**

Charge injection to change resonant wavelength

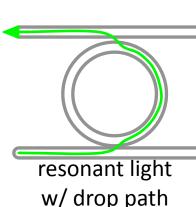

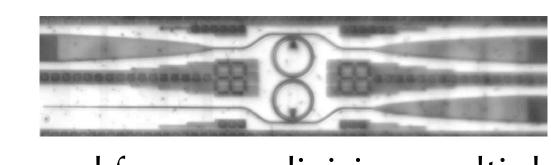

## **Ring Filter**

- Filter used for wave-division multiplexing • Use two cascaded rings to get additional frequency selectivity

- Elect Core Core Core L1 L1 L1 L1 Shared L2 Memory

# **Designing Multi-Socket Systems Using Silicon Photonics** Scott Beamer, Chris Batten, Ajay Joshi (MIT), Krste Asanović, Vladimir Stojanović (MIT)

| chnology Comparison              |          |               |                   |

|----------------------------------|----------|---------------|-------------------|

|                                  |          | Electric      | Photonic          |

| nergy                            | On-chip  | 50fJ/mm       | 150fJ*            |

|                                  | Off-chip | 5000fJ        | 150fJ*            |

| Delay                            | On-chip  | 100ps/mm      | 200ps + 10ps/mm   |

|                                  | Off-chip | 50ps + 5ps/mm | 200ps + 5ps/mm    |

| BW<br>ensity                     | On-chip  | 5 Gb/s/um     | 160 (320) Gb/s/um |

|                                  | Off-chip | 0.2 Gb/s/um   | 13 (26) Gb/s/um   |

| ctrical based on 22nm projection |          |               |                   |

## Silicon Photonics Summary

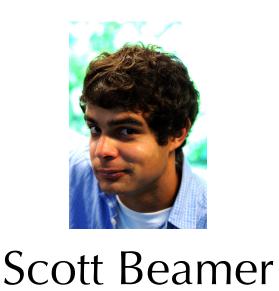

• Photonic links excel over a distance since conversion cost is constant • Photonic links are energy efficient off-chip • Once conversion cost is paid, link can go seamlessly on and off chip

• Path layout on-chip can greatly impact power

### **Design** Goals

• Connect cores to memory controllers • High and uniform bandwidth • Use photonic advantage to overbuild

• Single photonic hop - best use of technology • Co-design on and off chip networks to best use seamless links

### **Topology Insights**

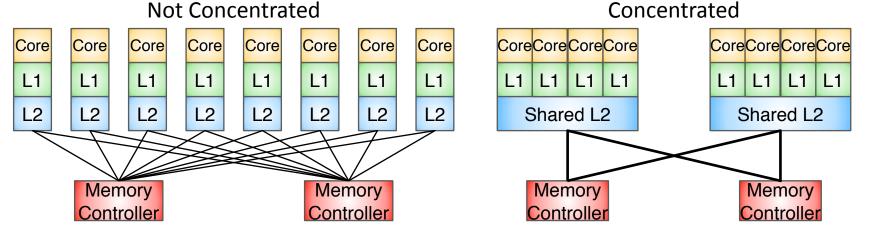

#### Concentation Not Concentrated

Concentration improves link utilization and reduces serialization latency

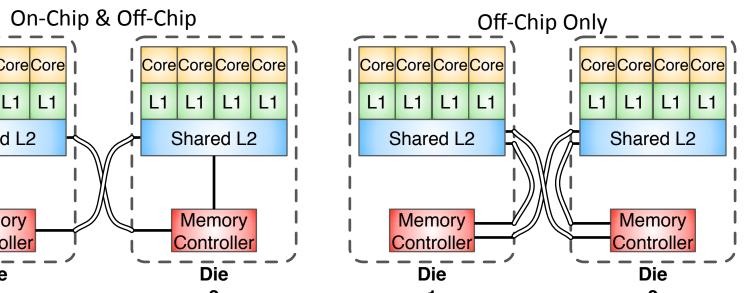

### Connections Off-Chip

• When changing number of sockets, all changes localized to off-chip where easier to change • Enables scalable system to have uniform bandwidth

• Group fibers by source (memory controller or cores)