# **Exploring the Tradeoffs between Programmability and Efficiency in Data-Parallel Accelerators**

YUNSUP LEE, University of California at Berkeley RIMAS AVIZIENIS, University of California at Berkeley ALEX BISHARA, University of California at Berkeley RICHARD XIA, University of California at Berkeley DEREK LOCKHART, Cornell University CHRISTOPHER BATTEN, Cornell University KRSTE ASANOVIĆ, University of California at Berkeley

We present a taxonomy and modular implementation approach for data-parallel accelerators, including the MIMD, vector-SIMD, subword-SIMD, SIMT, and vector-thread (VT) architectural design patterns. We introduce Maven, a new VT microarchitecture based on the traditional vector-SIMD microarchitecture, that is considerably simpler to implement and easier to program than previous VT designs. Using an extensive design-space exploration of full VLSI implementations of many accelerator design points, we evaluate the varying tradeoffs between programmability and implementation efficiency among the MIMD, vector-SIMD, and VT patterns on a workload of compiled microbenchmarks and application kernels. We find the vector cores provide greater efficiency than the MIMD cores, even on fairly irregular kernels. Our results suggest that the Maven VT microarchitecture is superior to the traditional vector-SIMD architecture, providing both greater efficiency and easier programmability.

Categories and Subject Descriptors: C.1.2 [**Processor Architectures**]: Multiple Data Stream Architectures—array and vector processors, MIMD, SIMD

General Terms: Design

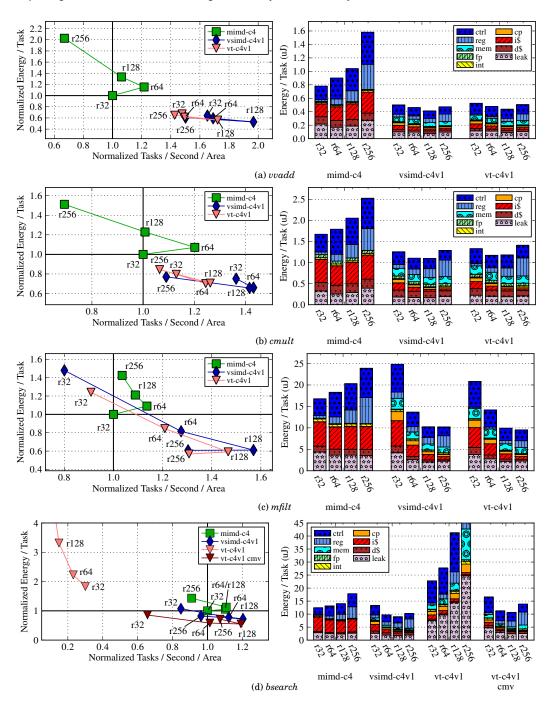

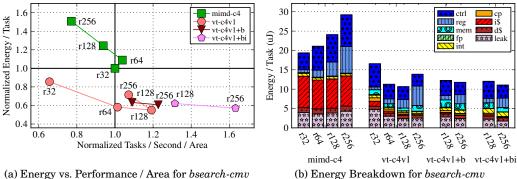

#### **ACM Reference Format:**

Lee, Y., Avizienis, R., Bishara, A., Xia, R., Lockhart, D., Batten, C., Asanović, K. 2011. Exploring the Trade-offs between Programmability and Efficiency in Data-Parallel Accelerators. ACM Trans. Comput. Syst. 9, 4, Article 39 (March 2010), 38 pages.

## 1. INTRODUCTION

Data-parallel kernels dominate the computational workload in a wide variety of demanding application domains, including graphics rendering, computer vision, audio processing, physical simulation, and machine learning. Specialized data-parallel accelerators [Wawrzynek et al. 1996; Kozyrakis et al. 1997; Gschwind et al. 2006; Krashinsky et al. 2004; NVIDIA 2009; Kelm et al. 2009] have long been known to provide greater energy and area efficiency than general-purpose processors for codes with significant amounts of data-level parallelism (DLP). With continuing improvements in

This work was supported in part by Microsoft (Award #024263) and Intel (Award #024894, equipment donations) funding and by matching funding from U.C. Discovery (Award #DIG07-10227).

Author's addresses: Y. Lee and R. Avizienis and A. Bishara and R. Xia and K. Asanović, Department of Electrical Engineering and Computer Science, University of California at Berkeley; D. Lockhart and C. Batten, School of Electrical and Computer Engineering, Cornell University.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies show this notice on the first page or initial screen of a display along with the full citation. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, to redistribute to lists, or to use any component of this work in other works requires prior specific permission and/or a fee. Permissions may be requested from Publications Dept., ACM, Inc., 2 Penn Plaza, Suite 701, New York, NY 10121-0701 USA, fax +1 (212) 869-0481, or permissions@acm.org.

© 2010 ACM 0734-2071/2010/03-ART39 \$10.00

DOI 10.1145/0000000.0000000 http://doi.acm.org/10.1145/0000000.0000000

39:2 Y. Lee et al.

transistor density and an increasing emphasis on energy efficiency, there has recently been growing interest in DLP accelerators for mainstream computing environments. These accelerators are usually attached to a general-purpose host processor, either integrated on the same die or on a separate die. The host processor executes system code and non-DLP application code while distributing DLP kernels to the accelerator. Surveying the wide range of data-parallel accelerator cores in industry and academia reveals a general tradeoff between programmability (how easy is it to write software for the accelerator?) and efficiency (energy/task and tasks/second/area). In this paper, we examine multiple alternative data-parallel accelerators to quantify the efficiency impact of microarchitectural features intended to simplify programming or expand the range of code that can be executed.

We first introduce a set of five architectural design patterns for DLP cores in Section 2, qualitatively comparing their expected programmability and efficiency. The MIMD pattern [Kelm et al. 2009] flexibly supports mapping data-parallel tasks to a collection of simple scalar or multithreaded cores, but lacks mechanisms for efficient execution of regular DLP. The vector-SIMD [Russel 1978; Wawrzynek et al. 1996; Kozyrakis et al. 1997] and subword-SIMD [Frankovich and Peterson 1957; Gschwind et al. 2006] patterns can significantly reduce the energy on regular DLP, but can require complicated programming for irregular DLP. The single-instruction multiple-thread (SIMT) [Lindholm et al. 2008] and vector-thread (VT) [Krashinsky et al. 2004] patterns are hybrids between the MIMD and vector-SIMD patterns that attempt to offer alternative tradeoffs between programmability and efficiency.

When reducing these high-level patterns to an efficient VLSI design, there is a large design space to explore. In Section 3, we present a common set of parameterized synthesizable microarchitectural components and show how these can be combined to form complete RTL designs for the different architectural design patterns, thereby reducing total design effort and allowing a fairer comparison across patterns. In this section, we also introduce Maven, a new VT microarchitecture. Our modular design strategy revealed a much simpler and more efficient VT implementation than the earlier Scale design [Krashinsky et al. 2004; Batten et al. 2004; Krashinsky 2007; Krashinsky et al. 2008]. Maven is based on a vector-SIMD microarchitecture with minimal changes to enable the improved programmability from VT [Batten 2010; Lee 2011; Lee et al. 2011], instead of the decoupled cluster microarchitecture of Scale. Another innovation in Maven is to use the same RISC ISA for both vector and scalar code, greatly reducing the effort required to develop an efficient VT compiler. The Scale design required a separate clustered ISA for vector code, which complicated compiler development [Hampton and Asanović 2008].

To concretely evaluate and compare the efficiency of these patterns, we used our parameterized microarchitectural components to generate hundreds of complete VLSI layouts for MIMD, vector-SIMD, and VT processors in a modern 65 nm technology. Section 4 describes our methodology for extracting the area, energy, and performance of these designs for a range of compiled microbenchmarks and application kernels.

Our results, presented in Section 5, show that vector cores are considerably more efficient in both energy and area-normalized performance than MIMD cores, although the MIMD cores are usually easier to program. Our results also suggest that the Maven VT microarchitecture is superior to the traditional vector-SIMD architecture, providing greater efficiency and a simpler programming model. For both VT and vector-SIMD, multi-lane implementations are usually more efficient than multi-core single-lane implementations and can be easier to program as they require less partitioning and load balancing. VT allows a flexible blend of vector-style or threaded-style programing, where efficiency increases as more vector features are used by software but programming effort increases correspondingly. Although we do not implement a

full SIMT machine, our initial analysis indicates SIMT will be considerably less efficient than VT for regular DLP code, whereas we expect SIMT and VT to be similar in efficiency for more irregular code programmed in a threaded style. Our belief is therefore that VT offers a wider tradeoff between efficiency and programmability than SIMT.

# 2. ARCHITECTURAL DESIGN PATTERNS FOR DATA-PARALLEL ACCELERATORS

Data-parallel applications can be categorized in two dimensions: the regularity with which data memory is accessed and the regularity with which the control flow changes. Regular data-level parallelism has well-structured data accesses where the addresses can be compactly encoded and are known well in advance of when the data is ready. Regular DLP also has well-structured control flow where the control decisions are either known statically or well in advance of when the control flow actually occurs. Irregular data-level parallelism might have less-structured data accesses where the addresses are more dynamic and difficult to predict, and might also have less-structured control flow with data-dependent control decisions. Irregular DLP might also include a small number of inter-task dependencies that force a portion of each task to wait for previous tasks to finish. Eventually a DLP kernel might become so irregular that it is better categorized as exhibiting *task-level parallelism*.

Figure 1 uses a few simple loops to illustrate the spectrum from regular to irregular DLP. The regular loop in Figure 1(a) includes unit-stride accesses (A[i],C[i]), strided accesses (B[2\*i]), and shared accesses (x). The loop in Figure 1(b) uses indexed accesses (E[C[i]],D[A[i]]). The loop in Figure 1(c) includes a data-dependent conditional to choose the correct shared constant, while the irregular loop in Figure 1(d) includes conditional accesses (B[i],C[i]) and computation. Finally, the irregular loop in Figure 1(e) includes an inner loop with a complex data-dependent exit condition.

There have been several studies which demonstrate that full DLP applications contain a mix of regular and irregular DLP [Sankaralingam et al. 2003; Krashinsky et al. 2004; Rivoire et al. 2006; Mahesri et al. 2008]. There are many reasons to prefer accelerators that can handle a wider variety of DLP over those which are restricted to just regular DLP. First, it is possible to improve performance and energy-efficiency even on irregular DLP. Second, even if the performance and energy-efficiency on irregular DLP is similar to a general-purpose processor, by keeping the work on the accelerator we make it easier to exploit regular DLP inter-mingled with irregular DLP. Finally, a consistent way of mapping both regular and irregular DLP simplifies the programming methodology. The rest of this section presents five architectural patterns for the design of data-parallel accelerators, and describes how each pattern handles both regular and irregular DLP.

```

for ( i = 0; i < n; i++ )

for (i = 0; i < n; i++)

C[i] = x * A[i] + B[2*i];

E[C[i]] = D[A[i]] + B[i];

for ( i = 0; i < n; i++ )

C[i] = false; j = 0;

(a) Regular DA & Regular CF

(b) Irregular DA & Regular CF

while ( !C[i] & (j < m) )

if ( A[i] == B[j++] )

for ( i = 0; i < n; i++ )

for (i = 0; i < n; i++)

C[i] = true;

x = (A[i] > 0) ? y : z;

if ( A[i] > 0 )

C[i] = x * A[i] + B[i];

C[i] = x * A[i] + B[i];

(e) Irregular DA & Irregular CF

(c) Regular DA & Irregular CF

(d) Irregular DA & Irregular CF

```

Fig. 1. Different Types of Data-Level Parallelism - Examples expressed in a C-like pseudocode and are ordered from regular DLP (i.e., regular data access (DA) and control flow (CF)) to irregular DLP (i.e., irregular data access (DA) and control flow (CF)).

39:4 Y. Lee et al.

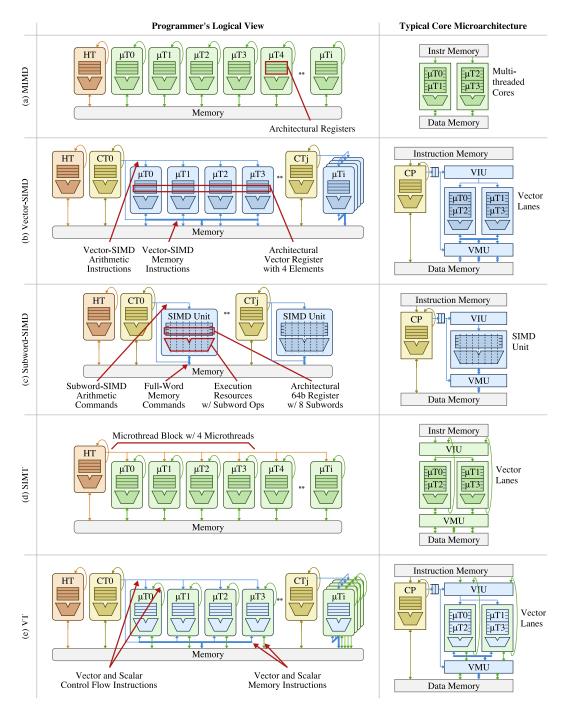

Fig. 2. Architectural Design Patterns – Programmer's logical view and a typical core microarchitecture for five patterns: (a) MIMD, (b) vector-SIMD, (c) subword-SIMD, (d) SIMT, and (e) VT. HT = host thread, CT = control thread, CP = control processor,  $\mu T$  = microthread, VIU = vector issue unit, VMU = vector memory unit.

```

1 div

m, n, nthr

1 load

x, x_ptr

1 br.gte tidx, n, done

1 load

x, x_ptr

2

mul

t, m, tidx

2 mov.sv VZ. x

3

add

a_ptr, t

3 loop:

3 add

a_ptr, tidx

3

add

4 setvl

vlen, n

4 load a, a_ptr

4 loop:

4

b_ptr, t

add

c_ptr, t

5 load.v VA, a_ptr

br.eq a, 0, done

5 setvl

vlen, n

6 load.v VB, b_ptr

6

6 load.v VA, a_ptr

6

7 cmp.gt.v VF, VA, 0

7 load.v VB, b_ptr

sub

t, nthr, 1

7 add

b_ptr, tidx

7

8 mov.sv VD, c_ptr

8

br.neq t, tidx, ex

8 add

c_ptr, tidx

9 mul.sv VT, x, VA, VF

9

rem

m, n, nthr

9

9 fetch.v ut_code

10 load

10 ex:

10 add.vv VC, VT, VB, VF

10

11 load

x. x ptr

11 store.v VC, c_ptr, VF

11 load

b, b_ptr

11 add

a ptr. vlen

12 mul

12 add

b_ptr, vlen

t, x, a

12

12

13 add

a_ptr, vlen

13 add

c_ptr, vlen

13 add

13 loop:

c, t, b

14

load

a, a_ptr

14 add

b_ptr, vlen

14 store c, c_ptr

14

15

br.eq a, 0, done

15 add

c_ptr, vlen

15 done:

15 sub

n, vlen

16

16

16 br.neq n, 0, loop

(c) SIMT

17 load

b, b_ptr

17 sub

17 ...

18 mul

t, x, a

18 br.neq n, 0, loop

18

19

add

c, t, b

19 ut code:

(b) Vector-SIMD

20

store c, c_ptr

20 br.eq a, 0, done

21

21 mul

t, z, a

22 done:

22 add

c, t, b

Fig. 3. Pseudo-Assembly for Irregular DLP Ex-

23

add

a_ptr, 1

23 add

d. tidx

ample - Pseudo-assembly implements the loop in Fig-

b_ptr. 1

24

add

24 store

c, d

ure 1(d) for the (a) MIMD, (b) vector-SIMD, (c) SIMT,

25

add

c_ptr, 1

25 done:

and (d) VT patterns. Assume *_ptr and n are inputs. Vi =

26

26 stop

vector register i, VF = vector flag register, *.v = vector

27

sub

(d) VT

command, *.vv = vector-vector op, *.sv = scalar-vector

br.neq m, 0, loop

op, nthr = number of uTs, tidx = current microthread's

(a) MIMD

```

index.

The multiple-instruction multiple-data (MIMD) pattern is perhaps the simplest approach to building a data-parallel accelerator. A large number of scalar cores are replicated across a single chip, and these scalar cores can be extended to support per-core multithreading to help improve performance by hiding various latencies. Figure 2(a) shows the programmer's logical view and an example implementation for the multithreaded MIMD pattern. All of the design patterns include a host thread (HT) as part of the programmer's logical view. The HT runs on the general-purpose processor and is responsible for application startup, configuration, interaction with the operating system, and managing the data-parallel accelerator. We refer to the threads that run on the data-parallel accelerator as microthreads (µTs), since they are lighter weight than the threads which run on the general-purpose processor. Programmers can map each data-parallel task to a separate microthread. The primary advantage of the MIMD pattern is the flexible programming model, and since every hardware microthread can execute a fully independent task, there should be little difficulty in mapping both regular and irregular DLP applications. This can simplify parallel programming compared to the other design patterns, but the primary disadvantage is that this pattern lacks any dedicated DLP mechanisms and hence it is difficult to gain an energy-efficiency advantage when executing DLP applications.

The pseudo-assembly in Figure 3(a) illustrates how we might map a portion of a simple irregular loop in Figure 1(d) to each uT. The first ten instructions divide the work among the µTs such that each thread works on a different consecutive partition of the input and output arrays. Notice that all uTs redundantly load the shared scalar value x (line 11). This might seem trivial in this instance, but the lack of specialized mechanisms to handle shared loads and other shared computation adversely impacts many regular DLP codes. Similarly there are no specialized mechanisms to take advantage of the regular data accesses. Figure 4(a) shows an execution diagram corresponding to the pseudo-assembly in Figure 3(a) running on the 2-core, 4-µT implementation with 39:6 Y. Lee et al.

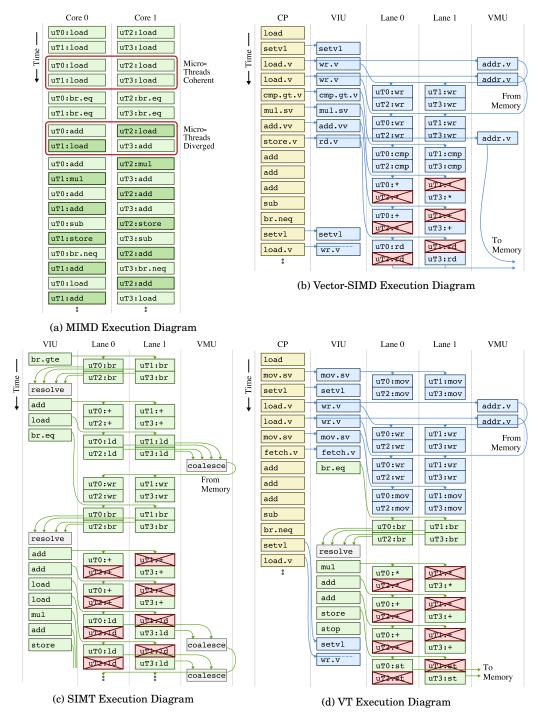

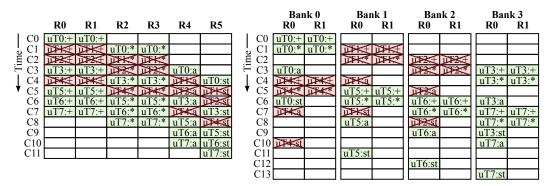

Fig. 4. **Execution Diagrams for Irregular DLP Example** – Executions are for the loop in Figure 1(d) for the (a) MIMD, (b) vector-SIMD, (c) SIMT, and (d) VT patterns. CP = control processor, VIU = vector issue unit, VMU = vector memory unit.

two-way multithreading illustrated in Figure 2(a). The scalar instructions from each μT are interleaved in a fixed pattern. It is very natural to map the data-dependent conditional to a scalar branch (line 15) which simply skips over the unnecessary work when possible. It is also straight-forward to implement conditional loads and stores of the B and C arrays by simply placing them after the branch. The execution diagram shows how the uTs are coherent (execute in lock-step) before the branch and then diverge after the data-dependent conditional with uT0 and uT3 quickly moving on to the next iteration. After a few iterations the uTs will most likely be completely diverged.

The Illinois Rigel is a recently proposed data-parallel accelerator following the MIMD pattern with 1024-cores and a single µT per core [Kelm et al. 2009]. Sun's line of Niagara processors exemplify the multithreaded MIMD pattern with 8-16 cores and 4–8 threads per core for a total of 32–64 threads per chip [Kongetira et al. 2005; Nawathe et al. 2007], but are not specifically designed as data-parallel accelerators. Niagara threads are heavier-weight than µTs, and Niagara is meant to be a standalone processor as opposed to a true coprocessor. Even so, the Niagara processors are often used to execute both regular and irregular DLP codes, and their multithreading enables good performance on these codes [Williams et al. 2009]. MIMD accelerators can be programmed using general-purpose parallel programming frameworks such as OpenMP [OpenMP 2008] and Intel's Thread Building Blocks [Reinders 2007], or in the case of Rigel, a custom task-based framework is used [Kelm et al. 2009].

In the vector single-instruction multiple-data (vector-SIMD) pattern a control thread (CT) uses vector memory instructions to move data between main memory and vector registers, and vector arithmetic instructions to operate on vectors of elements at once. As shown in Figure 2(b), one way to think of this pattern is as if each CT manages an array of µTs that execute in lock-step; each µT is responsible for one element of the vector and the hardware vector length is the number of uTs (e.g., four in Figure 2(b)). In this context, μTs are sometimes referred to as virtual processors [Zagha and Blelloch 1991. Unlike the MIMD pattern, the HT in the vector-SIMD pattern only interacts with the CTs and does not directly manage the µTs. Even though the HT and CTs must still allocate work at a coarse-grain amongst themselves via software, this configuration overhead is amortized by the hardware vector length. The CT in turn distributes work to the µTs with vector instructions enabling very efficient execution of fine-grain DLP. In a typical vector-SIMD core, the CT is mapped to a control processor (CP) and the uTs are mapped both spatially and temporally across one or more vector lanes in the vector unit. The vector memory unit (VMU) handles executing vector memory instructions, and the vector issue unit (VIU) handles the dependency checking and eventual dispatch of vector arithmetic instructions.

Figures 3(b) shows the pseudo-assembly corresponding to the loop in Figure 1(d). Unit-stride vector memory instructions (lines 5-6,11) efficiently move consecutive blocks of data in and out of vector registers. A vector-vector arithmetic instruction (line 10) efficiently encodes a regular arithmetic operation across the full vector of elements, and a combination of a scalar load and a scalar-vector instruction (lines 1,9) can easily handle shared accesses. In the vector-SIMD pattern the hardware vector length is not fixed by the instruction set but is instead stored in a special control register. The setvl instruction [Asanović 1998] takes the application vector length (n) as an input and writes the minimum of the application vector length and the hardware vector length to the given destination register vlen (line 4). As a side-effect, the setvl instruction sets the active vector length which specifies how many of the µTs are active and should participate in a vector instruction. Software can use the setvl instruction to process the vectorized loop in blocks equal to the hardware vector length, a process known as *stripmining*, without knowing what the actual hardware vector length is at compile time. A single binary can run on many different implementations with varying 39:8 Y. Lee et al.

hardware vector lengths. The setvl instruction will naturally handle the final iteration when the application vector length is not evenly divisible by the hardware vector length; setvl simply sets the active vector length to be equal to the final remaining elements. Note that a vector flag is used to conditionally execute the vector multiply, addition, and store instructions (lines 9–11). More complicated irregular DLP with nested conditionals can quickly require many independent flag registers and complicated flag arithmetic [Smith et al. 2000].

Figure 4(b) shows the execution diagram corresponding to the pseudo-assembly in Figure 3(b) running on the two-lane, four-µT implementation depicted in Figure 2(b). The vector memory commands (lines 5-6,11) are broken into two parts: the address portion is sent to the VMU which will issue the request to memory while the register write/read portion is sent to the VIU. For vector loads, the register writeback portion waits until the data returns from memory and then controls writing the vector register file with two elements per cycle over two cycles. Notice that the VIU/VMU are decoupled from the vector lanes to allow the implementation to begin fetching new vector loads before previous loads are consumed [Espasa and Valero 1996]. The vector arithmetic operations (lines 7,9-10) are also processed two elements per cycle over two cycles. Note that some µTs are inactive because the corresponding vector flag is false. The time-multiplexing of multiple uTs on the same physical lane is an important aspect of the vector-SIMD pattern, and it is common to use a large vector register file to support longer vector operations stretching over many cycles. The reduced instruction-issue bandwidth requirements of long vector operations simplifies management of multiple vector functional units, allowing a single vector instruction issue per cycle to keep multiple vector functional units busy, unlike the scalar MIMD pattern which would require multiple instructions issued per cycle to keep multiple scalar functional units busy. Vector chaining is a common optimization to bypass element values between multiple vector functional units to increase execution overlap of dependent vector instructions. A final point is that the vector command queue between the control processor and the VIU allows the control thread to continue executing while the vector unit is still processing older vector instructions. This decoupling means the control thread can quickly work through the loop overhead instructions (lines 13-18) and start issuing the next iteration of the stripmine loop, including starting new vector loads on the VMU, as soon as possible.

Figures 3(b) and 4(b) illustrate three ways that the vector-SIMD pattern can improve energy efficiency: (1) some instructions are executed once by the CT instead of for each  $\mu$ T as in the MIMD pattern (lines 1,13–18); (2) for operations that the  $\mu$ Ts do execute (lines 5–11), the CP and VIU can amortize overheads such as instruction fetch, decode, and dependency checking over vlen elements; and (3) for memory accesses which the  $\mu$ Ts still execute (lines 5–6,11) the VMU can efficiently move data in large blocks.

The Cray-1 was the first machine to exemplify this pattern [Russel 1978], and other examples include T0 [Wawrzynek et al. 1996], VIRAM [Kozyrakis et al. 1997], the Cray X2 [Abts et al. 2007], and the NEC SX-9 [Soga et al. 2009]. Autovectorizing compilers are the standard way to program these systems [Allen and Kennedy 2001].

The **subword single-instruction multiple-data** (subword-SIMD) architectural pattern is shown in Figure 2(c). In this pattern, the "vector-like" unit is really a wide scalar datapath with standard scalar registers, often overlaid on a double-precision floating-point unit. The pattern leverages the existing scalar datapaths and registers to execute multiple narrow-width operations in a single cycle. Some subword-SIMD variants support bitwidths larger than the widest scalar datatype, in which case the datapath can only be fully utilized with subword-SIMD instructions. Other variants unify the CT and SIMD unit such that the same datapath is used for both control, scalar arithmetic, and subword-SIMD instructions.

Comparing subword-SIMD to vector-SIMD, we see that the former has short vector lengths that are exposed to software as wide fixed-width datapaths, whereas vector-SIMD has longer vector lengths exposed to software as a true vector of elements. In vector-SIMD, the vector length can be exposed in such a way that the same binary can run on many different implementations with varying hardware resources, while code for one subword-SIMD implementation is usually not portable to implementations with different widths. Subword-SIMD implementations typically lack the strided or gather-scatter memory operations common in vector-SIMD implementations, which substantially limits the range of codes that can be executed efficiently. Special within-register element permute instructions are usually provided to accelerate certain classes of code but are generally difficult to target with a compiler.

The first machine with subword-SIMD extensions was likely the Lincoln Labs TX-2 [Frankovich and Peterson 1957]. All popular commercial general-purpose processors have added subword-SIMD ISA extensions over time [Peleg and Weiser 1996; Raman et al. 2000; Lomont 2011; Lee 1996; Tremblay et al. 1996; Diefendorff et al. 2000; Gwennap 1996; Goodacre and Sloss 2005], but the IBM Cell processor is an example of a data-parallel accelerator specially designed around this pattern, with eight cores each including a unified 128-bit subword-SIMD datapath that can execute scalar operations as well as  $16 \times 8$ -bit,  $8 \times 16$ -bit,  $4 \times 32$ -bit, or  $2 \times 64$ -bit operations [Gschwind et al. 2006]. In terms of programming methodology, some compilers include optimization passes that can automatically vectorize regular DLP, but many compilers only include intrinsics for accessing subword-SIMD operations and these are not usually portable between architecture families. In this work, we do not consider the subword-SIMD pattern further as it cannot tackle a wide variety of data-parallel codes.

The **single-instruction multiple-thread** (SIMT) pattern is a hybrid pattern with a programmer's logical view similar to the MIMD pattern but an implementation similar to the vector-SIMD pattern. As shown in Figure 2(d), the SIMT pattern supports a large number of uTs but no CTs; the HT is responsible for directly managing the uTs (usually through specialized hardware mechanisms). A  $\mu T$  block is mapped to a SIMT core which contains vector lanes similar to those found in the vector-SIMD pattern. However, since there is no CT, the VIU is responsible for amortizing overheads and executing the uT's scalar instructions in lock-step when they are coherent. The VIU also manages the case when the uTs execute a scalar branch possibly causing them to diverge. The uTs can sometimes reconverge either through static hints in the scalar instruction stream added by software or through dynamic convergence mechanisms implemented in hardware. SIMT only has scalar loads and stores, but the VMU can include a hardware memory coalescing unit to dynamically detect when these scalar accesses can be converted into vector-like memory operations. The SIMT pattern usually exposes the concept of a µT block to the programmer, where barriers are sometimes provided for intra-block synchronization and where application performance depends heavily on the coherence and coalescing opportunities within a uT block.

The loop in Figure 1(d) maps to the SIMT pattern in a similar way as in the MIMD pattern except that each µT is usually only responsible for a single element as opposed to a range of elements (see Figure 3(c)). Since there are no control threads and thus nothing analogous to the vector-SIMD pattern's setv1 instruction, a combination of dedicated hardware and software is required to manage the stripmining. The host thread tells the hardware how many uT blocks are required for the computation and the hardware manages the case when the number of requested  $\mu T$  blocks exceeds that supported by the hardware, by scheduling blocks sequentially onto the available resources. In the common case where the application vector length is not statically guaranteed to be evenly divisible by the µT block size, each µT must use a scalar branch to verify that the computation for the corresponding element is necessary (line 1).

39:10 Y. Lee et al.

Figure 4(c) shows the execution diagram corresponding to the pseudo-assembly in Figure 3(c) for a two-lane, four-uT implementation shown in Figure 2(d). Scalar branch management corresponding to the branch at line 1 will be discussed later. Without a control thread, all four µTs redundantly perform address calculations (lines 3,7-8) and the actual scalar load instruction (lines 4,11) even though these are unit-stride accesses. The VMU dynamically checks all four addresses, and if they are consecutive, then the VMU coalesces these accesses into a single vector-like memory operation. Also notice that since there is no control thread to amortize the shared load at line 10, all four µTs must redundantly load x. The VMU may be able to dynamically coalesce this into one scalar load which is then broadcast to all four µTs. The VMU attempts to coalesce well-structured stores (line 14) as well as loads. Since the uTs are coherent when they execute the scalar multiply and addition instructions (lines 12-13), these should be executed with vector-like efficiencies by the VIU. After issuing the scalar branch corresponding to line 5, the VIU waits for the µT block to calculate the branch resolution based on each uT's scalar data. The VIU then turns these branch resolution bits into a dynamically generated vector flag, which is used to mask off inactive elements on either side of the branch. SIMT implementations differ in the details of handling μT divergence, but the overall approach is similar. In contrast to vector-SIMD (where the control processor is decoupled from the vector unit making it difficult to access the vector flag registers), SIMT can avoid fetching instructions when the vector flag bits are all zero. So if the entire uT block takes the branch at line 5, then the VIU can completely skip the instructions at lines 7-14 and start the µT block executing at the branch target. Also note that conditional memory accesses are naturally encoded by simply placing them after the branch (lines 10–11,14).

SIMT machines hide branch resolution and other latencies using hardware multithreading across multiple vectors of  $\mu$ Ts. This requires very large register files to hold multiple contexts, each with multiple vector registers.

Figures 3(c) and 4(c) illustrate some of the issues that can prevent the SIMT pattern from achieving vector-like energy-efficiencies on regular DLP. The  $\mu$ Ts must redundantly execute instructions that would otherwise be amortized onto the CT (lines 1–3,7–10). Regular data accesses are encoded as multiple scalar accesses (lines 4,11,14) which then must be dynamically transformed (at some energy overhead) into vector-like memory operations. In addition, the lack of a control thread requires every  $\mu$ T to perform stripmining calculations (lines 1) and prevents deep access-execute decoupling to efficiently tolerate long memory latencies. Even so, the ability to achieve vector-like efficiencies on coherent  $\mu$ T instructions helps improve SIMT energy-efficiency compared to the MIMD pattern. The real strength of the SIMT pattern, however, is that it provides a simple way to map complex data-dependent control flow with  $\mu$ T scalar branches (line 5).

The NVIDIA Fermi graphics processor is a modern example of this pattern with 32 SIMT cores each with 16 lanes suitable for graphics as well as more general data-parallel applications [NVIDIA 2009]. The Fermi SIMT core supports up to 32 hardware threads or warps, where each warp contains 32  $\mu$ Ts. Various SIMT frameworks such as Microsoft's DirectX Compute [Microsoft 2009], NVIDIA's CUDA [Nickolls et al. 2008], Stanford's Brook [Buck et al. 2004], and OpenCL [OpenCL 2008] allow programmers to write high-level code for the host thread and to specify the scalar code for each  $\mu$ T as a specially annotated function. A combination of off-line compilation, just-in-time optimization, and hardware actually executes each data-parallel kernel.

The **vector-thread** (VT) pattern is also a hybrid pattern but takes a very different approach from the SIMT pattern. As shown in Figure 2(e), the HT manages a collection of CTs and each CT in turn manages an array of  $\mu$ Ts. Similar to the vector-SIMD pattern, this allows various overheads to be amortized onto the CT, and control

threads can also execute vector memory commands to efficiently handle regular data accesses. Unlike the vector-SIMD pattern, the CT does not execute vector arithmetic instructions but instead uses a *vector-fetch instruction* to indicate the start of a scalar instruction stream that should be executed by the  $\mu Ts$ . The VIU allows the  $\mu Ts$  execute coherently, but as in the SIMT pattern, they can also diverge after executing scalar branches.

Figure 3(d) shows the VT pseudo-assembly corresponding to the loop in Figure 1(d). Stripmining (line 5), loop control (line 11–16), and regular data accesses (lines 6–7) are handled just as in the vector-SIMD pattern. Instead of vector arithmetic instructions, we use a vector-fetch instruction (line 9) with one argument which indicates the instruction address at which all µTs should immediately start executing (e.g., the instruction at the ut\_code label). All µTs execute these scalar instructions (lines 20–24) until they reach a stop instruction (line 26). An important part of the VT pattern is that the control thread views the scalar registers across multiple µTs as a single set of vector registers. In this example, the unit-stride vector load at line 6 writes the vector register VA with vlen elements. Each µT's scalar register a implicitly refers to that  $\mu$ T's element of vector register VA (i.e.,  $\mu$ TO's scalar register a implicitly refers to the first element of the vector register VA). The µTs cannot access the control thread's scalar registers, since this would significantly complicate control processor decoupling. A shared scalar value is instead broadcast by first loading a scalar value with the control thread (line 1) and then using a scalar-vector move instruction (lines 2,8) to copy the given scalar register value into each element of the given vector register. A scalar branch (line 20) is used to encode data-dependent control flow. The uTs thus completely skip the instructions at 21–24 when the branch condition is true. The conditional store is encoded by simply placing the store after the branch (line 24) similar to the MIMD and SIMT examples.

Figure 4(d) illustrates how the pseudo-assembly in Figure 3(d) would execute on the implementation pictured in Figure 2(e). An explicit scalar-vector move instruction (line 2) writes the scalar value into each element of the vector register two elements per cycle over two cycles. The unit-stride vector load instructions (lines 6–7) execute as in the vector-SIMD pattern. The control processor then sends the vector fetch instruction to the VIU. The VIU fetches the branch instruction (line 20) and issues it across the uTs. Similar to the SIMT pattern, the VIU waits until all  $\mu$ Ts resolve the scalar branch to determine how to proceed. If all  $\mu$ Ts either take or do not take the branch, then the VIU can simply start fetching from the appropriate address. If some  $\mu$ Ts take the branch while others do not, then the  $\mu$ Ts diverge and the VIU needs to keep track of which  $\mu$ Ts are executing which side of the branch.

Figures 3(d) and 4(d) illustrate how VT achieves vector-like energy-efficiency while maintaining the ability to flexibly map irregular DLP. Control instructions are executed by the control thread, either only once per loop (lines 1–2) or once per iteration (lines 11–16). A scalar branch (line 20) provides a convenient way to map complex data-dependent control flow. The VIU is still able to amortize instruction fetch, decode, and dependency checking for vector arithmetic instructions (lines 21–23). VT uses vector memory instructions to efficiently move blocks of data between memory and vector registers (lines 6–7). There are however some overheads including the extra scalar-vector move instruction (line 2), the vector-fetch instruction (line 9), and the  $\mu T$  stop instruction (line 26).

The Scale VT processor was the first example of the VT pattern [Krashinsky et al. 2004]. Scale's programming methodology uses either a combination of compiled code for the control thread and hand-coded assembly for the µTs, or a preliminary version of a vectorizing compiler written specifically for Scale [Hampton and Asanović 2008].

39:12 Y. Lee et al.

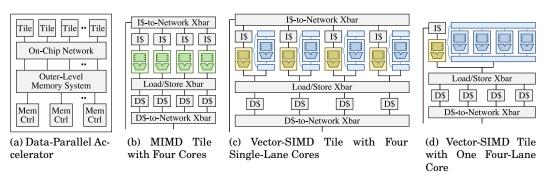

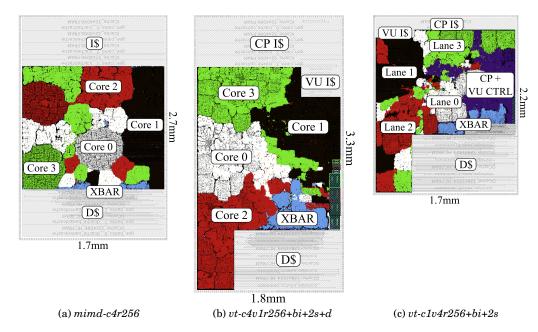

#### 3. MICROARCHITECTURE OF MIMD, VECTOR-SIMD, AND VT TILES

In this section, we describe in detail the microarchitectures used to evaluate the various patterns. A data-parallel accelerator will usually include an array of tiles and an on-chip network to connect them to each other and an outer-level memory system, as shown in Figure 5(a). Each tile includes one or more tightly coupled cores and their caches, with examples in Figure 5(b)–(d). In this paper, we focus on comparing the various architectural design patterns with respect to a single data-parallel tile. The inter-tile interconnect and memory system are also critical components of a DLP accelerator system, but are outside the scope of this work.

Fig. 5. Example Data-Parallel Tile Configurations

# 3.1. Microarchitectural Components

We developed a library of parameterized synthesizable RTL components that can be combined to construct MIMD, vector-SIMD and VT tiles. Our library includes long-latency functional units, a multi-threaded scalar integer core, vector lanes, vector memory units, vector issue units, and blocking and non-blocking caches.

A set of **long-latency functional units** provide support for integer multiplication and division, and IEEE single-precision floating-point addition, multiplication, division, and square root. These units can be flexibly retimed to meet various cycle-time constraints.

Our **scalar integer core** implements a RISC ISA, with basic integer instructions executed in a five-stage, in-order pipeline but with two sets of request/response queues for attaching the core to the memory system and long-latency functional units. A two-read-port/two-write-port (2r2w-port) 32-entry 32-bit register file holds both integer and floating-point values. One write port is for the integer pipeline and the other is shared by the memory system and long-latency functional units. The core can be multithreaded, with replicated architectural state for each thread and a dynamic thread scheduling stage at the front of the pipeline.

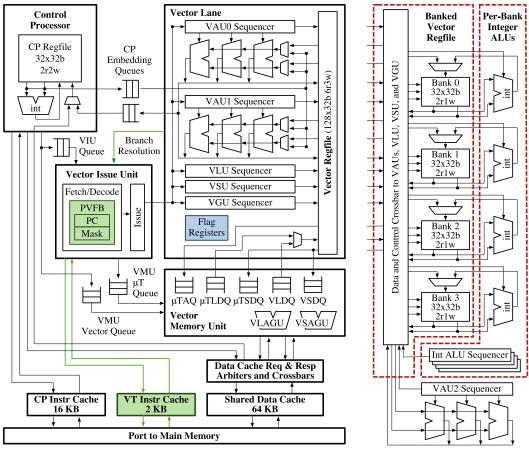

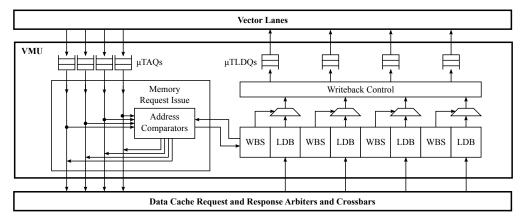

Figure 6 shows the microarchitectural template used for all the vector-based cores. A control processor (CP) sends vector instructions to the vector unit, which includes one or more vector lanes, a vector memory unit (VMU), and a vector issue unit (VIU). The lane and VMU components are nearly identical in all of the vector-based cores, but the VIU differs significantly between the vector-SIMD and VT cores as discussed below.

Our baseline **vector lane** consists of a unified 6r3w-port vector register file and five vector functional units (VFUs): two arithmetic units (VAUs), a load unit (VLU), a store unit (VSU), and an address-generation unit (VGU). Each VAU contains an integer ALU and a subset of the long-latency functional units. The vector register file can be

(a) Baseline Vector-SIMD and VT Core Microarchitecture

(b) Banked Regfile w/ Per-Bank Int ALUs

Fig. 6. Vector-Based Core Microarchitecture – (a) Each vector-based core includes one or more vector lanes, vector memory unit, and vector issue unit; PVFB = pending vector fragment buffer, PC = program counter, VAU = vector arithmetic unit, VLU = vector load-data writeback unit, VSU = vector store-data read unit, VGU = address generation unit for  $\mu T$  loads/stores, VLDQ = vector load-data queue, VSDQ = vector store-data queue, VLAGU/VSAGU = address generation unit for vector loads/stores,  $\mu TAQ = \mu T$  address queue,  $\mu TLDQ = \mu T$  load-data queue,  $\mu TSDQ = \mu T$  store-data queue. Modules specific to vector-SIMD or VT cores are highlighted. (b) Changes required to implement intra-lane vector register file banking with per-bank integer ALUs.

dynamically reconfigured to support between 4–32 registers per  $\mu T$  with corresponding changes in maximum vector length (32–1). Each VFU has a sequencer to step through elements of each vector operation, generating physical register addresses.

The **vector memory unit** coordinates data movement between the memory system and the vector register file using decoupling [Espasa and Valero 1996]. The CP splits each vector memory instruction into a vector memory upp issued to the VMU and a vector register access upp sent to the VIU, which is eventually issued to the VLU or VSU in the vector lane. A load upp causes the VMU to issue a vector's worth of load requests to the memory system, with data returned to the vector load data queue (VLDQ). As data becomes available, the VLU copies it from the VLDQ to the vector register file. A store upp causes the VMU to retrieve a vector's worth of data from the vector store

39:14 Y. Lee et al.

data queue (VSDQ) as it is pushed onto the queue by the VSU. Note that for single-lane configurations, the VMU still uses wide accesses between the VLDQ/VSDQ and the memory system, but moves data between the VLDQ/VSDQ and the vector lane one element at a time. Individual  $\mu T$  loads and stores (gathers and scatters) are handled similarly, except addresses are generated by the VGU and data flows through separate queues.

The main difference between vector-SIMD and VT cores is how the **vector issue unit** fetches instructions and handles conditional control flow. In a vector-SIMD core, the CP sends individual vector instructions to the VIU, which is responsible for ensuring that all hazards have been resolved before sending vector  $\mu$ 0 to the vector lane. Our vector-SIMD ISA supports data-dependent control flow using conventional vector masking, with eight single-bit flag registers. A  $\mu$ T is prevented from writing results for a vector instruction when the associated bit in a selected flag register is clear.

In our VT core, the CP sends vector-fetch instructions to the VIU. For each vector fetch, the VIU creates a new vector fragment consisting of a program counter, initialized to the start address specified in the vector fetch, and an active uT bit mask, initialized to all active. The VIU then fetches and executes the corresponding sequential instruction stream across all active  $\mu$ Ts, sending a vector  $\mu$ p plus active  $\mu$ T mask to the vector lanes for each instruction. The VIU handles a branch instruction by issuing a compare upp to one of the VFUs, which then produces a branch-resolution bit mask. If the mask is all zeros or ones, the VIU continues fetching scalar instructions along the fall-through or taken path. Otherwise, the µTs have diverged causing the VIU to split the current fragment into two fragments representing the µTs on the fall-through and taken paths respectively. The VIU then continues to execute the fall-through fragment while placing the taken fragment in a pending vector fragment buffer (PVFB). The µTs can repeatedly diverge, creating new fragments, until there is only one uT per fragment. The current fragment finishes when it executes a stop instruction. The VIU then selects another vector fragment from the PVFB for execution. Once the PVFB is empty, indicating that all the µTs have stopped executing, the VIU can begin processing the next vector-fetch instruction.

Our library also includes **blocking and non-blocking cache** components with a rich set of parameters: cache type (instruction/data), access port width, refill port width, cache line size, total capacity, and associativity. For non-blocking caches, additional parameters include the number of miss-status-handling registers (MSHR) and the number of secondary misses per MSHR.

# 3.2. Constructing Tiles

MIMD cores combine a scalar integer core with integer and floating-point long-latency functional units, and support from one to eight  $\mu$ Ts per core. **Vector cores** use a single-threaded scalar integer core as the CP connected to either a vector-SIMD or VT VIU, with one or more vector lanes and a VMU. To save area, the CP shares long-latency functional units with the vector lane, as in the Cray-1 [Russel 1978].

We constructed two tile types: **multi-core tiles** consist of four MIMD (Figure 5(b)) or single-lane vector cores (Figure 5(c)), while **multi-lane tiles** consist of a single CP connected to a four-lane vector unit (Figure 5(d)). All tiles have the same number of long-latency functional units. Each tile includes a shared 64-KB four-bank data cache (8-way set-associative, 8 MSHRs, 4 secondary misses per MSHR), interleaved by 64-byte cache line. Request and response arbiters and crossbars manage communication between the cache banks and cores (or lanes). Each CP has a 16-KB private instruction cache and each VT VIU has a 2-KB vector instruction cache. Hence the overall instruction cache capacity (and area) is much larger in multi-core (64–72 KB) as compared to multi-lane (16–18 KB) tiles.

# 3.3. Microarchitectural Optimizations: Banking and Density-Time Execution

We explored a series of microarchitectural optimizations to improve performance, area, and energy efficiency of our baseline vector-SIMD and VT cores. The first was using a conventional **banked vector register file** to reduce area and energy (see Figure 6(b)). While a monolithic 6r3w register file simplifies vector lane design by allowing each VFU to access any element on any clock cycle, the high port count is expensive. Dividing the register file into four independent banks each with one write and two read ports significantly reduces register file area while keeping capacity constant. A crossbar connects banks to VFUs. The four 2r1w banks result in a greater aggregate bandwidth of eight read and four write ports, which we take advantage of by adding a third VAU (VAU2) to the vector lane and rearranging the assignment of functional units to VAUs.

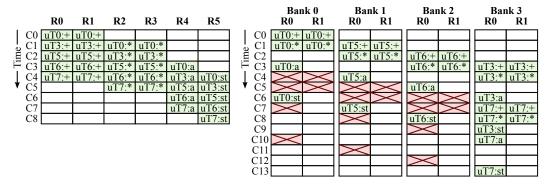

Figure 7(a) illustrates an example read port scheduling with a monolithic 6r3w vector register file. The add  $\mu$ op is issued at cycle 0 to use read ports R0 and R1 for eight cycles. The multiply  $\mu$ op is scheduled to access its operands with R2 and R3 starting at cycle 1.  $\mu$ TAQ and  $\mu$ TSDQ access  $\mu$ ops for a  $\mu$ T store instruction are performed through R4 and R5 at cycle 3 and 4 respectively. Figure 7(b) illustrates how the read

(a) Monolithic 6r3w Vector Register File

(b) Banked Vector Register File (Four 2r1w Banks)

(c) Monolithic VRF with Density-Time Execution

(d) Banked VRF with Density-Time Execution

Fig. 7. **Example Read Port Scheduling** – All four examples execute an add, a multiply, a  $\mu$ TAQ access, and a  $\mu$ TSDQ access  $\mu$ 0p. A hardware vector length of eight, and an active  $\mu$ T mask of 11101001 is assumed. VRF = vector register file, R = read port, C = cycle, + = addition, \* = multiplication, a =  $\mu$ TAQ access, st =  $\mu$ TSDQ access.

39:16 Y. Lee et al.

port scheduling changes with vector regfile banking. Registers within a  $\mu T$  are colocated within a bank, and  $\mu Ts$  are striped across banks. As a VFU sequencer iterates through the  $\mu Ts$  in a vector, it accesses a new bank on each clock cycle. The VIU must schedule vector  $\mu$ ops to prevent bank conflicts, where two VFUs try to access the same bank on the same clock cycle. Note that the  $\mu TSDQ$  access cannot be scheduled at cycle 4 because of a bank conflict with the add operation. The operation is instead scheduled at cycle 6, requiring a total of 14 cycles to finish—2 cycles longer than a monolithic vector register file. Read ports are simply disabled for inactive  $\mu Ts$  ( $\mu T1$ ,  $\mu T2$ , and  $\mu T4$ ) in both cases.

We developed another optimization for the banked design, which removes integer units from the VAUs and instead adds four **per-bank integer ALUs** directly connected to the read and write ports of each bank, bypassing the crossbar (see Figure 6(b)). This saves energy, and also helps performance by avoiding structural hazards and increasing peak integer throughput to four integer VAUs. The area cost of the extra ALUs is small relative to the size of the register file.

We also investigated **density-time execution** [Smith et al. 2000] to improve vector performance on irregular codes. The baseline vector machine takes time proportional to the vector length for each vector instruction, regardless of the number of inactive μTs. For example, if the hardware vector length is 8, it will take 8 cycles to execute a vector instruction, even if only five uTs are active (Figure 7(a)). Codes with highly irregular control flow often cause significant divergence between the uTs, splintering a vector into many fragments of only a few active µTs each. Density-time improves vector execution efficiency by "compressing" the vector fragment and only spending cycles on active µTs. With density-time execution in Figure 7(c), it only takes 5 cycles per vector fragment rather than 8 cycles. As illustrated in Figure 7(d), bank scheduling constraints reduce the effectiveness of density-time execution in banked register files. Rather than compressing inactive uTs from the whole vector, only inactive uTs from the same bank can be compressed. In Figure 7(d), uT3 and uT7 from the same bank are both active, resulting in no actual cycle savings with density-time execution. Multilane machines have even greater constraints, as lanes must remain synchronized, so we only added density-time execution to our single-lane configurations.

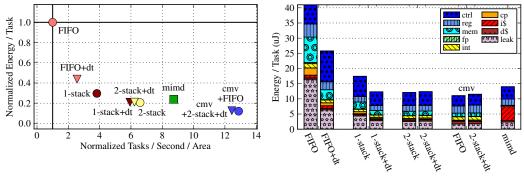

#### 3.4. Microarchitectural Optimizations: Dynamic Fragment Convergence

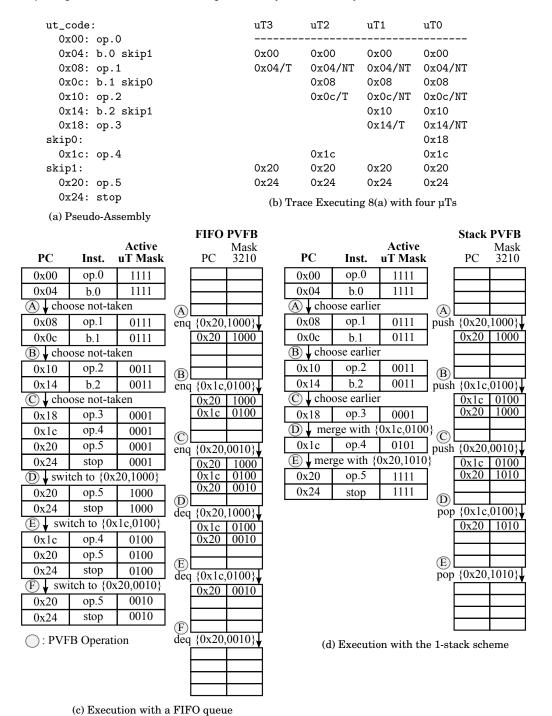

The PVFB in our baseline VT machine is a FIFO queue with no means to merge vector fragments. Figure 8(c) shows the execution of code in Figure 8(a) with the baseline FIFO queue. We assume a hardware vector length of four, and the outcome of branches b.0, b.1, and b.2 for all four  $\mu$ Ts are shown as part of the execution trace in Figure 8(b). The execution starts at the vector-fetched PC (0x00) with an active  $\mu$ T bit mask, initialized to all active (1111). Since op.0 is not a branch instruction, the FIFO vector fragment selection policy chooses the PC+4 fragment, which consists of a PC (0x04) and the same  $\mu$ T mask (1111), for execution. Once branch b.0 is resolved, the selection policy chooses to stash the taken fragment {0x20,1000} in the PVFB for later execution and execute the not-taken fragment {0x08,0111}. Vector fragments {0x1c,0100} and {0x20,0010} are saved next as a result of branches b.1 and b.2. Once the current fragment {0x24,0001} encounters a stop instruction, the selection policy chooses to dequeue a fragment from the PVFB to execute. Note that once a vector becomes fragmented, those fragments will execute independently until all  $\mu$ Ts execute a stop instruction, even when fragments have the same PC (0x20).

To improve execution efficiency, we developed two schemes to implement **dynamic fragment convergence** in the PVFB for VT machines. When a new fragment is inserted into the PVFB, both schemes will attempt to dynamically merge the fragment with an existing fragment if their PCs match, OR-ing their active µT masks together.

Fig. 8. **Executing Irregular DLP Code with Forward Branches Only** – Example (a) pseudo-assembly, (b) trace (PCs are aligned to match the 1-stack scheduling), (c) execution diagram illustrating how the FIFO queue manages divergence, (d) execution diagram illustrating how the 1-stack scheme manages divergence. T = taken, NT = not-taken, PVFB = pending vector fragment buffer.

39:18 Y. Lee et al.

| loop:                 | uT3     | uT2     | uT1     | uT0     |

|-----------------------|---------|---------|---------|---------|

| 0x00: op.0            |         |         |         |         |

| 0x04: b.0 skip        | 0x00    | 0x00    | 0x00    | 0x00    |

| 0x08: op.1            | 0x04/T  | 0x04/NT | 0x04/T  | 0x04/T  |

| skip:                 |         | 80x0    |         |         |

| 0x0c: b.1 loop        | 0x0c/T  | 0x0c/T  | 0x0c/NT | 0x0c/NT |

| 0x10: op.2            |         |         | 0x10    | 0x10    |

| 0x14: b.2 loop        |         |         | 0x14/T  | 0x14/T  |

| 0x18: op.3            | 0x00    | 0x00    | 0x00    | 0x00    |

| 0x1c: stop            | 0x04/NT | 0x04/NT | 0x04/NT | 0x04/NT |

| (a) Pseudo-Assembly   | 80x0    | 80x0    | 80x0    | 80x0    |

| (a) I seudo-rissembly | 0x0c/NT | 0x0c/NT | OxOc/NT | 0x0c/NT |

|                       | 0x10    | 0x10    | 0x10    | 0x10    |

|                       | 0x14/NT | Ox14/NT | Ox14/NT | 0x14/NT |

|                       | 0x18    | 0x18    | 0x18    | 0x18    |

|                       | 0x1c    | 0x1c    | 0x1c    | 0x1c    |

|                       |         |         |         |         |

<sup>(</sup>b) Trace Executing 9(a) with four  $\mu Ts$

(c) Execution with the 1-stack scheme

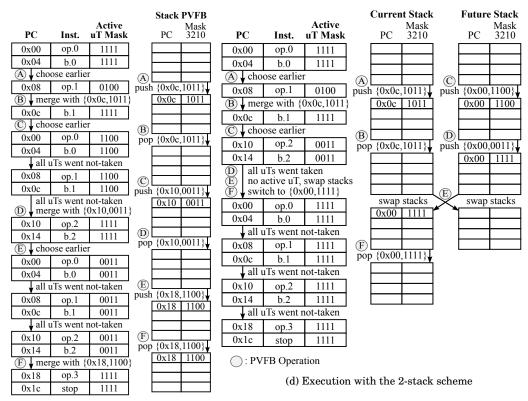

Fig. 9. **Executing Irregular DLP Code with Backward Branches** – Example (a) pseudo-assembly, (b) trace (PCs are aligned to match the 2-stack scheduling), (c) execution diagram illustrating how the 1-stack scheme manages divergence, (d) execution diagram illustrating how the 2-stack scheme manages divergence. T = taken, NT = not-taken, PVFB = pending vector fragment buffer.

The challenge is to construct a fragment scheduling heuristic that maximizes opportunities for convergence by avoiding early execution of fragments which could later have been able to merge with other fragments in the PVFB.

Our first convergence scheme, called *1-stack*, organizes the PVFB as a stack with fragments sorted by PC address, with newly created fragments systolically insertion-sorted into the stack. The stack vector fragment selection policy always picks the fragment with the numerically smallest (earliest) PC among the taken and not-taken fragments, merging with the fragment at the top of the PVFB stack when possible. The intuition behind 1-stack is to favor fragments trailing behind in execution, giving them more chance to meet up with faster-moving fragments at a convergence point. The execution diagram in Figure 8(d) illustrates the 1-stack fragment scheduling heuristic. Note that when fragment  $\{0x1c,0100\}$  is pushed to the stack, the stack enforces PC ordering and keeps that fragment on the top. Also note fragment  $\{0x20,0010\}$  is merged with an existing fragment in the stack with the same PC 0x20. Once PC 0x1c is reached, the current fragment is merged with the fragment at the top of the stack  $\{0x1c,0100\}$ , resulting in a new fragment  $\{0x1c,0101\}$  to execute. Note that the operations at PC 0x20 are now executed with all  $\mu$ Ts active.

The 1-stack scheme performs reasonably well, but is sub-optimal for loops with multiple backwards branches. Fragments which first branch back for another loop iteration are treated as if they are behind slower fragments in the same iteration and race ahead. Suppose four  $\mu$ Ts execute the pseudo-assembly in Figure 9(a) and the four  $\mu$ Ts pick branch directions as shown in Figure 9(b). An execution diagram in Figure 9(c) illustrates this phenomenon. As shown in the diagram,  $\mu$ T2 and  $\mu$ T3 satisfies a loop condition such that b.1 is taken. Since the 1-stack scheme favors the smallest PC, these  $\mu$ T fragments are executed to completion, only converging with the fragment at PC 0x10 on the last iteration. This reduces the number of active  $\mu$ Ts per instruction execution (instructions at PC 0x00-0x14 are executed with an active  $\mu$ T mask 0011) yielding sub-optimal execution for this type of code.

To solve this problem, our second scheme, called 2-stack, divides the PVFB into two virtual stacks, one for fragments on the current iteration of a loop and another for fragments on a future iteration of a loop (Figure 9(d)). Fragments created by the forward branch ( $\{0x0c,1011\}$ ) are pushed onto the current stack, while fragments created by backwards branches ( $\{0x00,1100\}$  and  $\{0x00,0011\}$ ) are pushed onto the future stack. The selection policy now only pops fragments from the current stack. When the current stack empties, the current and future stacks are swapped (PVFB operation E). The 2-stack implementation is similar to the 1-stack implementation, but PCs saved in the PVFB have an extra most-significant bit added to be used in comparisons for sorting. This bit is set if the fragment being inserted into the PVFB was a backwards branch to prevent this fragment from being chosen until all fragments on the current iteration are executed. Once no fragments of the current iteration remain, this bit is toggled so that the next iteration's fragments become active candidates for selection. Implementing the 2-stack scheme in this way allows us to physically use only one stack, exploiting the fact that we can never use more entries than there are  $\mu$ Ts.

Note that the Maven VT design only uses dynamic information such as the PC of a fragment, with no explicit static hints to aid fragment convergence as are believed to be used in SIMT architectures [NVIDIA 2009; Fung et al. 2009]. The stack-based convergence scheme proposed in [Woop et al. 2005] and described in [Fung et al. 2009] uses immediate postdominators as explicit yield points to guide convergence in the warp scheduler. To know the immediate postdominator of a diverging branch, however, the control flow graph needs to be analyzed. [Fung et al. 2009] proposes dynamic warp formation to increase the utilization of the SIMD pipeline. Five scheduling polices were considered to maximize the number of active threads when dynamically

39:20 Y. Lee et al.

forming a warp. Among the five schemes, the program counter (DPC) policy is similar to the 1-stack convergence scheme. The intuition behind two schemes are the same: the program counter is a good indicator of fragment progress.

# 3.5. Microarchitectural Optimizations: Dynamic Memory Coalescer

The final optimization we considered is a **dynamic memory coalescer** for multi-lane VT vector units (Figure 10). During the execution of a  $\mu$ T load instruction, each lane may generate a separate memory address on each cycle. The memory coalescer compares the high-order bits of each memory address across lanes and combines matching requests. The low-order bits or each request address are stored as word and byte select bits alongside the load data buffer. The number of low-order bits should match the maximum size of the memory response in bytes. When memory responses arrive from the cache, we use the stored word and byte select bits to select the correct portion of the response to write to each uT load data queue feeding the vector lanes.

For example, support the four µT address queues issue the following load word requests: 0x001c, 0x0014, 0x0008, 0x0014. We assume each data cache response may contain up to sixteen bytes, and that cache banks are interleaved on sixteen-byte boundaries. The address comparators identify that the first, second, and fourth requests may be coalesced. The second and fourth requests are disabled from accessing the cache, while the first request is annotated with extra information that indicates that it is a coalesced request for the first, second, and fourth lanes. The third request passes through to a separate cache bank alone. At the same time, the address comparators write the word and byte select information to the word and byte select buffers. In this case the first, second, and fourth requests select the fourth, second, and second words of the sixteen-byte coalesced response, respectively. Notice how addresses need not be in ascending order and may even match in the low-order bits.

Additional control logic must be added to the data cache arbiter to correctly route memory responses. The arbiter must be able to write a response to multiple load data buffers but only if all buffers are ready to receive data. A conflict occurs when a coalesced response arrives at the same time as a non-coalesced response and both wish to write to the same load data buffer. This introduces more complex control dependencies between vector lanes.

Fig. 10. **Memory Coalescer Microarchitecture** – A memory coalescer for multi-lane VT tiles with four lanes. VMU = vector memory unit,  $\mu TAQ = \mu T$  address queue,  $\mu TLDQ = \mu T$  load data queue, WBS = word/byte select buffer, LDB = load data buffer.

Dynamic memory coalescing can significantly help performance on codes that use  $\mu T$  loads to access memory addresses with a unit stride, as these would otherwise generate cache bank conflicts. Similarly, codes which use  $\mu T$  loads to access the same memory address also benefit. This effect diminishes with larger strides, as requests no longer occupy the same cache bank. Compared to vector memory operations, however,  $\mu T$  memory operations are still less efficient for code with regular memory access patterns even with dynamic memory coalescing. Vector memory operations have the benefit of access-execute decoupling because addresses can be computed independently and far ahead of non-memory operations. Compile-time generation of unit-stride and constant-stride vector memory operations supports hardware coalescing much more efficiently than dynamic comparison of  $\mu T$  memory addresses at run time. However, dynamic coalescing of  $\mu T$  memory accesses can improve the efficiency of irregular access patterns with high spatial locality, and could also improve indexed memory operations on traditional vector machines. We compare the effectiveness of vector memory operations to using only  $\mu T$  memory operations with memory coalescing in Section 5.3.

#### 4. EVALUATION FRAMEWORK

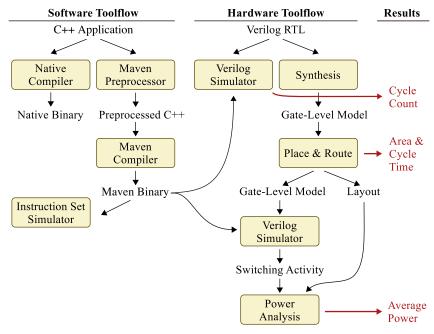

This section describes the software and hardware infrastructure used to evaluate the various microarchitectural options introduced in the previous section, and also outlines the specific configurations, microbenchmarks, and application kernels used in our evaluation. Figure 11 illustrates the overall process of compiling C++ application code into a binary, generating a VLSI layout from an RTL description of a particular machine configuration, and simulating the execution of the application to extract area, performance, and power statistics.

Fig. 11. **Evaluation Framework** – The software toolflow allows C++ applications to be compiled either natively or for Maven, while the hardware toolflow transforms the Verilog RTL for a data-parallel tile into actual layout. From this toolflow we can accurately measure area, performance  $(1/\text{cycle count} \times \text{cycle time})$ , and energy (average power  $\times$  cycle count  $\times$  cycle time).

39:22 Y. Lee et al.

# 4.1. Programming Methodology

Past accelerators usually relied on hand-coded assembly or compilers that automatically extract DLP from high-level programming languages [Bacon et al. 1994; De-Vries and Lee 1995; Hampton and Asanović 2008]. Recently there has been a renewed interest in explicitly data-parallel programming methodologies [Nickolls et al. 2008; OpenCL 2008; Buck et al. 2004], where the programmer writes code for the HT and annotates data-parallel tasks to be executed in parallel on all  $\mu Ts$ . We developed a similar explicit-DLP C++ programming environment for Maven. Supporting such a programming style for our VT implementation was made relatively easy by the use of a single ISA for the CT and  $\mu Ts$ . The software toolflow is illustrated on the left-hand side of Figure 11. Note that to aid in debugging, we produce a program binary that runs natively on our development platform along with the binary for our target machine architecture. For all systems, a simple proxy kernel running on the cores supports basic system calls by communicating with an application server running on the host. More details about the programming methodology can be found in [Batten 2010].

To bring up a reasonable compiler infrastructure with limited resources, we leveraged a standard scalar compiler. We started with a recent version of the GNU assembler, linker, and C++/newlib compiler (version 4.4.1), which all contain support for the basic MIPS32 instruction set. We then modified the assembler to support the new Maven scalar and vector instructions.

Most of our efforts went into modifying the compiler back-end. We first unified the integer and floating-point register space. Instruction templates were added for the new divide and remainder instructions, since the Maven ISA lacks high and low registers. Branch delay slots were also removed. A new vector register space and the corresponding instruction templates required for register allocation were added. Some of these modifications were able to leverage the GNU C++ compiler's built-in support for fixed-length subword-SIMD instructions. Compiler intrinsics were added for some of the vector instructions to enable software to explicitly generate these instructions and for the compiler to understand their semantics. The control thread and the  $\mu Ts$  have different performance characteristics, so we leveraged the compiler instruction scheduling framework to create two pipeline models for Maven: one optimized for control threads and the other optimized for  $\mu Ts$ .

There were relatively few modifications necessary to the compiler front-end. We used the GNU C++ compiler's function attribute framework to add new attributes denoting functions meant to run on the  $\mu Ts$  for performance tuning. We again leveraged the GNU C++ compiler's built-in support for fixed-length subword-SIMD instructions to create true C++ vector types.

Figure 12 illustrates how the irregular DLP loop in Figure 1(d) might be coded for various architectural patterns. Figure 12(a) illustrates how the MIMD architectural pattern is programmed. The VT architectural pattern can be programmed much like a SIMT machine (Figure 12(b)), in which case programming is relatively easy but execution is less efficient. The VT pattern also allows programmers to expend more effort in optimizing their code to hoist structured memory accesses out as vector memory operations, and to use scalar operations (Figure 12(c)), which provides more efficiency than is possible with a pure SIMT machine. Figure 12(d) shows how irregular DLP is mapped to the Vector-SIMD architectural pattern. Finally, Figure 12(e) describes how we leverage the MIMD programming model to target a multi-core VT machine.

For MIMD, a "master"  $\mu T$  on the multithreaded core is responsible for spawning the work on the other remaining "worker"  $\mu Ts$ . To support this, we first modify the proxy kernel to support multiple threads of execution and then build a lightweight user-level threading library called *bthreads*, which stands for "bare threads", on top of the

```

1

void idlp_mimd( int c[], int a[], int b[],

void idlp_vt_simt( int c[], int a[], int b[],

int n, int x )

int n, int x )

2

3

3

BTHREAD_PARALLEL_RANGE( n, (c,a,b,x),

4

int blocksz = vt::config( 11, n );

int nblocks = ( size + blocksz - 1 ) / blocksz;

5

for ( int i = range.begin();

6

6

i < range.end(); i++ ) {</pre>

vt::HardwareVector<int*> vap(a),vbp(b),vcp(c);

if (a[i] > 0 )

vt::HardwareVector<int*> vxp(&x);

c[i] = x * a[i] + b[i];

vt::HardwareVector<int> vsize(size);

9

vt::HardwareVector<int> vbsz(blocksz);

10

10

11

}));

11

for ( int bidx = 0: bidx < nblocks: bidx++ ) {

12

12

vt::HardwareVector<int> vbidx(bidx);

13

(a) MIMD

14

VT_VFETCH( (vxp,vap,vbp,vcp,vsize,vbsz,vbidx),

15

16

({

int idx = vbidx * vbsz + vt::get_utidx();

17

if ( idx < vsize ) {</pre>

18

19

if ( vap[idx] > 0 )

1

void idlp_vt( int c[], int a[], int b[],

vcp[idx] = (*vxp) * vap[idx] + vbp[idx];

2

int n, int x)

21

3

22

}));

int vlen = vt::config( 7, n );

23

4

vt::HardwareVector<int> vx(x);

5

24

vt::sync_cv(); // vector memory fence

}

6

25

7

for ( int i = 0; i < n; i += vlen ) {

vlen = vt::set_vlen(n-i); // stripmining

(b) VT in SIMT fashion

9

vt::HardwareVector<int*> vcp(&c[i]);

10

vt::HardwareVector<int> va, vb;

11

void idlp_vsimd( int c[], int a[], int b[],

12

int n, int x )

13

va.load(&a[i]); // unit-stride vector load

14

vb.load(&b[i]); // unit-stride vector load

int vlen = vt::config( 9, n );

15

vt::HardwareVector<int> vx(x);

VT_VFETCH( (vcp,vx,va,vb),

16

17

({

for ( int i = 0; i < n; i += vlen ) {

if ( va > 0 )

18

vlen = vt::set_vlen(n-i); // stripmining

19

vcp[vt::get_utidx()] = vx * va + vb;

20

10

vt::HardwareVector<int> vctmp;

21

vt::HardwareVector<int> va, vb, vc;

11

vt::sync_cv(); // vector memory fence

22

12

23

va.load(&a[i]); // unit-stride vector load

13

vb.load(&b[i]); // unit-stride vector load

14

(c) VT

15

vc.load(&c[i]); // unit-stride vector load

17

asm (

"slt.f.vv flag1, vzero, [va]

n"

18

n"

19

"mul.vv %[vctmp], %[vx], %[va]

void idlp_mc_vt( int c[], int a[], int b[],

20

"add.vv %[vctmp], %[vctmp], %[vb] \n"

int n, int x )

"mov.vv %[vc], %[vctmp], $flag1

2

21

3

: [vctmp] "=&Z"(vctmp)

// outputs

22

BTHREAD_PARALLEL_RANGE( n, (c,a,b,x),

4

: [va] "Z"(va), [vx] "Z"(vx), // inputs

23

[vb] "Z"(vb), [vc] "Z"(vc)

24

idlp_vt( &c[range.begin()],

25

&a[range.begin()],

26

&b[range.begin()],

8

27

vc.store(&c[i]); // unit-stride vector store

range.size(), x );

28

10

}));

29

vt::sync_cv(); // vector memory fence

}

30

(e) Multi-core VT

(d) Vector-SIMD

```

Fig. 12. **Irregular DLP Example using Maven Programming Methodology** – Code corresponds to the loop in Figure 1(d). Roughly, code (a) compiles to assembly in Figure 3(a), code (c) compiles to assembly in Figure 3(d), and code (d) compiles to assembly in Figure 3(b).

39:24 Y. Lee et al.

proxy-kernel threads. There is one bthread for each underlying hardware uT context. The application is responsible for managing scheduling. Parallel threads are spawned using a BTHREAD\_PARALLEL\_RANGE macro as shown in Figure 12(a). This macro automatically partitions the input dataset's linear index range, creates a separate function, spawns the function onto each µT, passes in arguments through memory, and waits for the threads to finish. Each thread does the work from range.begin() to range.end() where range is defined by the preprocessor macro to be different for each thread. Line 4 specifies the total number of elements to be distributed to the worker µTs and a list of C++ variables that should be marshalled for each worker µT. The final argument to the macro is the work to be done by each µT (lines 5-11). The work can contain any of the other architectural design pattern programming methodologies to enable mapping an application to multiple cores. As illustrated in Figure 12(e), by calling the idlp\_vt function inside the body of a BTHREAD\_PARALLEL\_RANGE macro we can use the bthreads library to distribute work amongst multiple VT cores. This programming model is similar to the OpenMP programming framework [OpenMP 2008], where the programmer explicitly annotates the source code with pragmas to mark parallel loops.

Figure 12(b) illustrates the Maven VT programming environment used in SIMT fashion. The config function on line 4 takes two arguments: the number of required μT registers and the application vector. This function returns the actual number of μTs supported by the hardware (block size), which is used to calculate the number of uT blocks on line 5. Lines 7–8 copy array base pointers and address of x, and lines 9-10,13copy size, block size, and block index into all µTs. A for loop on line 12 emulates multiple µT blocks mapped to the same core. The VT\_VFETCH macro on lines 15-22 takes two arguments: a list of hardware vectors, and the actual code, which should be executed on each µT. The code within the vector-fetched block specifies what operations to perform on each element of the hardware vectors. This means that the C++ type of a hardware vector is different inside versus outside the vector-fetched block. Outside the block, a hardware vector represents a vector of elements and has type Hardware Vector <T> (e.g., vsize on line 9 has type HardwareVector<int>), but inside the block, a hardware "vector" now actually represents a single element and has type T (e.g., vsize on lines 18 has type int). Code within a vector-fetched block can include almost any C++ language feature including stack-allocated variables, object instantiation, templates, conditionals (if, switch), and loops (for, while). The primary restrictions are that a vector-fetched block cannot use C++ exceptions nor make any system calls. After calculating its own index on line 15, a conditional on line 16 checks to make sure the index is not greater than the array size. Lines 19–20 contain the actual work. Line 24 performs a memory fence to ensure that all results are visible in memory before returning from the function. Note that this is similar to the CUDA programming methodology [Nickolls et al. 2008]. The address calculation on line 17 and the conditional branch on line 18 closely follows the CUDA programming practice (compare voidx with CUDA blockIdx.x, vbsz to blockDim.x, and vt::get\_utidx() to threadIdx.x).

Figure 12(c) shows an example of code after optimizing for the VT architectural pattern. The output of the config function is now used to stripmine across the application vector via the for loop on line 7. The call to set\_vlen on line 8 allows the stripmine loop to naturally handle cases where size is not evenly divisible by the hardware vector length. This eliminates the first conditional branch in Figure 12(b) to check whether the index is in bounds. Line 5 instantiates a hardware vector containing elements of type int and initializes all elements in the vector with the scalar value x. This shared variable will be kept in the same hardware vector across all iterations of the stripmine loop. The structured memory accesses are turned into unit-stride loads (line 11,13–14); vlen consecutive elements of arrays a and b are moved into the appropriate hardware vector with the load member function. Note that the conditional store is implemented

similarly to Figure 12(b); the base pointer for the array c is copied into all elements of the hardware vector vcp on line 10 and then a scalar store (line 19) is executed inside a conditional.

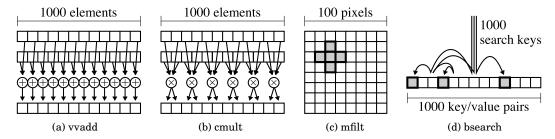

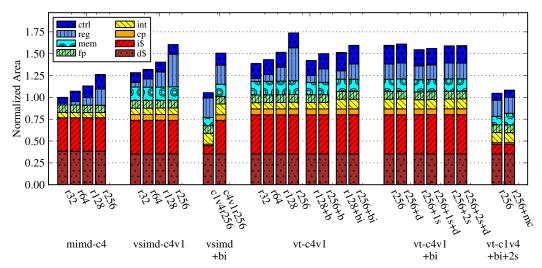

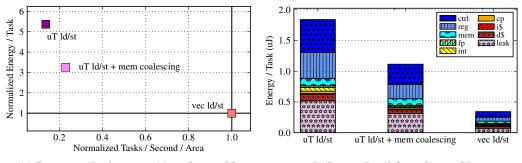

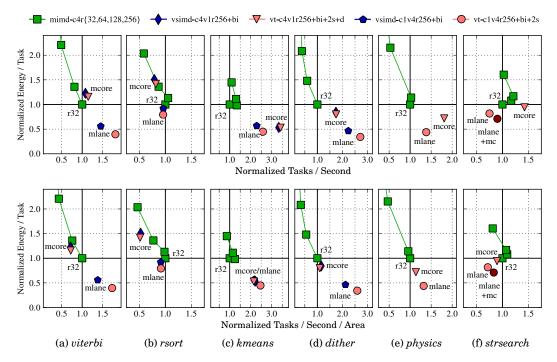

For vector-SIMD, we were able to leverage the built-in GCC vectorizer for mapping very simple regular DLP microbenchmarks, but the GCC vectorizer could not automatically compile the larger application kernels for the vector-SIMD tiles. For these more complicated vector-SIMD kernels, we use a subset of our VT C++ library for stripmining and vector memory operations along with GCC's inline assembly extensions for the actual computation. Figure 12(d) shows how the existing VT programming environment is used with hand-coded assembly to map an irregular DLP loop to a vector-SIMD machine. The same stripmining process is used on lines 4–8. Lines 13-14 are the same unit-stride loads used in the VT programming model. The actual computation is expressed with an inline assembly extension found on lines 17-25. Note that a conditional store is implemented with a unit-stride load (line 15), a conditional move (line 21), and a unit-stride store (line 27).